# LILLIPUT-AE: a New Lightweight Tweakable Block Cipher for Authenticated Encryption with Associated Data

Submission to the NIST Lightweight Cryptography Standardization Process

Alexandre Adomnicai<sup>1</sup>, Thierry P. Berger<sup>2</sup>, Christophe Clavier<sup>2</sup>, Julien Francq<sup>3</sup>, Paul Huynh<sup>4</sup>, Virginie Lallemand<sup>4</sup>, Kévin Le Gouguec<sup>3</sup>, Marine Minier<sup>4</sup>, Léo Reynaud<sup>2</sup>, and Gaël Thomas<sup>5</sup>

<sup>1</sup>Trusted Objects - Europarc de Pichaury, Bât. B8, 1330 rue Guillibert de la Lauzière, 13290 AIX-EN-PROVENCE - France, email: a.adomnicai@trusted-objects.com

<sup>2</sup>Université de Limoges - 123 avenue Albert Thomas, 87060 LIMOGES Cedex - France, email: thierry.berger, christophe.clavier, leo.reynaud@xlim.fr

<sup>3</sup>Airbus CyberSecurity - ZA Clef Saint-Pierre, 1 Bd Jean Moulin, CS 40001, MetaPole, 78996 ELANCOURT Cedex - France, email: julien.francq,

kevin.legouguec@airbus.com

<sup>4</sup>Université de Lorraine, CNRS, Inria, LORIA - Campus Scientifique - BP 239, 54506 VANDOEUVRE-LES-NANCY - France, email: paul.huynh, virginie.lallemand, marine.minier@loria.fr

<sup>5</sup>DGA Maîtrise de l'information - BP 7, 35998 RENNES CEDEX 9 - France, email: gael.thomas.87@gmail.com

Corresponding Submitter's Name: Julien Francq

Email: julien.francq@airbus.com Telephone: (+33) 1 61 38 71 39 Organization: Airbus CyberSecurity

Postal Address: Airbus CyberSecurity - ZA Clef Saint-Pierre, 1 Bd Jean Moulin, CS 40001, MetaPole, 78996 ELANCOURT Cedex - France

Backup Point of contact: Marine Minier Email: marine.minier@loria.fr Telephone: (+33) 6 87 10 68 58

Organization: Université de Lorraine, CNRS, Inria, LORIA

Postal Address: Université de Lorraine, CNRS, Inria, LORIA - Campus Scientifique - BP 239, 54506 VANDOEUVRE-LES-NANCY - France

website: https://paclido.fr/lilliput-ae/

# Contents

| 1 | Intr            | roduction                                                                                                                                                                                                                                                                           | 3                                      |

|---|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2 | Spe 2.1 2.2 2.3 | The Tweakable Block Cipher LILLIPUT-TBC                                                                                                                                                                                                                                             | 5<br>6<br>6<br>10<br>13<br>13<br>15    |

| 3 | Des             | sign Rationale and Security Analysis                                                                                                                                                                                                                                                | 20                                     |

| J | 3.1             | Design Rationale of the Modes of Operation 3.1.1 $\Theta$ CB3                                                                                                                                                                                                                       | 20<br>20<br>20<br>21<br>21<br>22       |

|   | 3.3             | Security Analysis of the Modes of Operation                                                                                                                                                                                                                                         | 25<br>27<br>27<br>27<br>27             |

|   | 3.4             | Security Analysis of Lilliput-TBC  3.4.1 Differential / Linear Cryptanalysis  3.4.2 Related Tweakey Boomerang Attacks  3.4.3 Structural Attacks  3.4.4 Division Property  3.4.5 Subspace Cryptanalysis  3.4.6 Algebraic Attacks  3.4.7 Differential Fault Analysis in Middle Rounds | 27<br>28<br>29<br>30<br>31<br>31<br>31 |

| 4 | Imp 4.1         | Software Implementations 4.1.1 Round Function OneRoundEGFN 4.1.2 Tweakey Schedule 4.1.3 Possible Trade-Offs 4.1.4 16-bit and 32-bit Platforms 4.1.5 Performance Benchmarks Summary                                                                                                  | 35<br>35<br>36<br>41<br>41<br>42<br>46 |

|   | 4.2             | Hardware Implementations                                                                                                                                                                                                                                                            |                                        |

| 5 | Ack | nowled | Igments                             | 54 |

|---|-----|--------|-------------------------------------|----|

|   | 4.4 | Future | Works                               | 53 |

|   |     | 4.3.3  | Performance Impact                  | 53 |

|   |     | 4.3.2  | Application to the Entire Algorithm | 52 |

|   |     | 4.3.1  | The S-box                           | 49 |

|   | 4.3 | Thresh | old Implementations                 | 49 |

|   |     | 4.2.2  | VHDL Results                        | 4  |

# Chapter 1

# Introduction

In this submission to the NIST Lightweight Cryptography Standardization Process, we present a new Authenticated Encryption with Associated Data (AEAD) scheme LILLIPUT-AE based on the tweakable block cipher LILLIPUT-TBC which is itself based on the classical block cipher LILLIPUT presented in [6] with a modified tweakey schedule.

We define two particular authenticated encryption modes: LILLIPUT-I and LILLIPUT-II based respectively on the two modes  $\Theta$ CB3 [38] and SCT-2 used in Deoxys [33] for both. The  $\Theta$ CB3 mode is a nonce-respecting mode whereas SCT-2 is a nonce-misuse resistant mode.

From those two authenticated encryption modes LILLIPUT-I and LILLIPUT-II, we derive several sets of parameters that conform with the NIST Submission Requirements and Evaluation Criteria for the Lightweight Cryptography Standardization Process. Our primary member is LILLIPUT-II-128.

As shown in the next chapters, LILLIPUT-AE is an authenticated encryption scheme that provides full 128-bit, 192-bit or 256-bit security level. It performs well in software and also in hardware. Moreover, the underlying block cipher LILLIPUT has been extensively studied by the cryptographic community [53, 40, 51] and no weakness has been exhibited for the full version of LILLIPUT.

We are convinced that extending LILLIPUT, a well-studied lightweight block cipher, to an 8-bit oriented version and combining it with a mode with good performances and with reinforced security, is a good answer regarding both efficiency and security to the expectations of the NIST standardization process.

## Main Features of LILLIPUT-AE. From our point of view, LILLIPUT-AE brings many advantages:

- It is based on building schemes (authenticated encryption modes, encryption process) that have been significantly studied by the cryptographic community. Moreover, the security of these blocks has been strengthened by modifying some parameters (e.g., more secure S-box and tweakey schedule).

- Its primary member is a nonce-misuse resistant mode, which allows an easier management of cryptographic components deployed on the field.

- Its software implementations on 8-bit (e.g., Atmel AVR ATmega128 microcontrollers) and 16-bit (e.g., Texas Instruments MSP430F1611 microcontrollers) platforms are very competitive. In terms of execution time (which relates to power consumption), and for 128-bit keys, LILLIPUT-AE is comparable to lightweight winners of the CAESAR competition [16], ACORN and ASCON, on 8-bit platforms, and is significantly faster on 16-bit platforms.

- Its hardware implementations on FPGA platforms (e.g., Xilinx Spartan-6) are more compact than ACORN and ASCON. Moreover, straightforward ASIC implementations of LILLIPUT-AE lead to at most around 5000 Gate Equivalents (GEs) for its maximum parameter sizes. Serial implementations will decrease this figure down to 4000 GEs or 3000 GEs depending on the parameter sizes, which is equivalent to serial implementations of plain AES without authentication mode.

- Some degrees of freedom are given to the implementers of LILLIPUT-AE: for some operations (e.g., in the tweakey schedule), they can trade code size for RAM usage and execution time. Some operations can also be tabulated to accelerate their computation.

- The design facilitates side-channel protection: in particular, the S-box of LILLIPUT-AE has been chosen to optimize its cost in threshold implementations.

- A first fault injection analysis of LILLIPUT-AE shows that faulting 7 rounds or more from the end of the algorithm requires injecting too many faults (say millions) to be practical. A cautious recommendation is then to protect the last 7 rounds of LILLIPUT-AE against fault injection, which leads to a 22% execution time overhead if a straightforward duplication countermeasure is implemented.

Organization of the submission. In Chapter 2, we provide the complete specifications of our submission LILLIPUT-AE including the two considered modes of authenticated encryption with associated data LILLIPUT-I and LILLIPUT-II (Section 2.2) and the tweakable block cipher LILLIPUT-TBC with its particular tweakey schedule (Section 2.3).

In Chapter 3, we detail our design choices: first for the modes (Section 3.1) and second for the tweakable block cipher (Section 3.2). We also perform an extensive security analysis of these two parts in Section 3.3 and in Section 3.4.

In Chapter 4, we give the implementation results we obtain for both software platforms and hardware platforms.

# Chapter 2

# Specifications

This chapter presents the full specifications of our submission to the NIST Lightweight Cryptography Standardization Process. More precisely, we present our new Authenticated Encryption with Associated Data (AEAD) scheme LILLIPUT-AE.

After introducing notations and the sets of parameters, we introduce in Section 2.2 the two particular authenticated encryption modes: LILLIPUT-I based on the nonce-respecting mode  $\Theta$ CB3 and LILLIPUT-II based on the nonce-misuse resistant mode SCT-2.

Then, in Section 2.3, we introduce our tweakable block cipher LILLIPUT-TBC used in both LILLIPUT-I and LILLIPUT-II.

**Notations.** Let us introduce the following notations: K will represent the key of length k bits, P the plaintext of length n bits, T the tweak of length t bits and we denote by  $E_K(T, P)$  the ciphering process using the tweakable block cipher  $E_K^T$ .

The concatenation operation at binary level is represented by || and  $pad10^*$  is the function that applies the  $10^*$  padding on n bits, i.e.  $pad10^*(X) = X||1||0^{n-|X|-1}$  when |X| < n. For an empty string  $\epsilon$ , the  $10^*$  padding will not add any bit:  $pad10^*(\epsilon) = \epsilon$ . The truncation of the word X to the first i bits is given by  $[X]_i$ , and the truncation to the last i bits by  $[X]_i$ . To emphasize a string X is of length n, we may write it  $X_{(n)}$ . We denote by  $\gg i$  and  $\ll i$  respectively the right and left shifts of i bits, and by  $\gg i$  and  $\ll i$  the right and left rotations of i bits.

We will also denote by  $S^{\gg i}$  and  $S^{\ll i}$  the binary matrices of size  $8 \times 8$  corresponding to a right shift by i bits positions or a left shift by i bits positions respectively. More precisely, and for example,

$$S^{\gg 1} = \begin{pmatrix} 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 & 0 & 0 \end{pmatrix} \text{ and } S^{\ll 1} = \begin{pmatrix} 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \end{pmatrix}$$

The encryption part  $\mathcal{E}$  takes as input a variable-length plaintext M (with m = |M| bits), a variable-length associated data A (with a = |A| bits), a fixed-length public nonce N and a k-bit key K (we deliberately used the same letter K to represent the key in the authenticated encryption scheme and the one in the tweakable block cipher, since they always refer to the same object). It outputs an m-bit ciphertext C and a  $\tau$ -bit tag, denoted tag (with  $\tau \in [0, \dots, n]$ ) i.e.  $(C, \text{tag}) = \mathcal{E}_K(N, A, M)$ .

The verification/decryption part  $\mathcal{D}$  takes as input a variable-length ciphertext C (with m = |C|), a  $\tau$ -bit tag, denoted tag (with  $\tau \in [0, \dots, n]$ ), a variable-length associated data A (with a = |A|), a fixed-length public nonce N and a k-bit key K. It outputs either an error string  $\perp$  to signify that the verification has failed, or an m-bit string  $M = \mathcal{D}_K(N, A, C, \text{tag})$  when the tag is valid.

The maximum message length (in n-bit blocks) is denoted  $max_l$  and the maximum number of messages that can be handled with the same key is denoted  $max_m$  (the same limitation applies to the associated data material).

## 2.1 Recommended Parameters

We derive our scheme LILLIPUT-AE into two authenticated encryption modes: LILLIPUT-I and LILLIPUT-II. LILLIPUT-I is a nonce-respecting mode corresponding with ΘCB3 and LILLIPUT-II is a nonce-misuse resistant mode corresponding with SCT-2.

The recommended parameter sets for all variants of these modes is given in table 2.1. These parameters have been chosen according to the internal tweakable block cipher LILLIPUT-TBC.

| Name            | k   | t   | n   | N   | au  |

|-----------------|-----|-----|-----|-----|-----|

| LILLIPUT-I-128  | 128 | 192 | 128 | 120 | 128 |

| Lilliput-I-192  | 192 | 192 | 128 | 120 | 128 |

| Lilliput-I-256  | 256 | 192 | 128 | 120 | 128 |

| LILLIPUT-II-128 | 128 | 128 | 128 | 120 | 128 |

| LILLIPUT-II-192 | 192 | 128 | 128 | 120 | 128 |

| LILLIPUT-II-256 | 256 | 128 | 128 | 120 | 128 |

Table 2.1: Recommended parameter sets for LILLIPUT-AE. Our primary member LILLIPUT-II-128 is in bold notation.

For both variants,  $max_m = 2^{|N|} = 2^{120}$  bits. However,  $max_l$  is dependent on the tweak input and thus differs from one variant to the other:

- in the encryption part of LILLIPUT-I, the tweak is a concatenation of a 4-bit prefix, the nonce N and the index of the message block, thus  $max_l = 2^{t-4-|N|}$  blocks.

- in the encryption part of LILLIPUT-II, the tweak is a concatenation of a 4-bit prefix and the index of the message block, thus  $max_l = 2^{t-4}$  blocks.

As a result, the maximum message length in bytes is  $2^{72}$  bytes for LILLIPUT-I and  $2^{128}$  bytes for LILLIPUT-II.

## 2.2 The Authenticated Encryption LILLIPUT-AE

In this section, we describe the authenticated encryption modes that are used in our proposal LILLIPUT-AE. These mode variants are similar to the two modes described in Deoxys [33]:

- LILLIPUT-I (Section 2.2.1): in this nonce-respecting variant, the same nonce N is expected to never be used twice with the same key for encryption.  $\mathcal{E}^I$  denotes the encryption part and  $\mathcal{D}^I$  the verification/decryption part.

- LILLIPUT-II (Section 2.2.2): in this variant, a nonce N may be reused with the same key for encryption.  $\mathcal{E}^{II}$  denotes the encryption part and  $\mathcal{D}^{II}$  the verification/decryption part.

As stated previously, 4-bit prefixes are used for the tweak input to separate the various types of encryption/authentication blocks, akin to what has been done in Deoxys [33].

## 2.2.1 Nonce-Respecting Mode: $\Theta$ CB3

This scheme follows the  $\Theta$ CB3 framework [38] and therefore directly benefits from this framework's proof of security regarding authentication and privacy. In this mode, the tweak length is 192 bits. The encryption algorithm  $\mathcal{E}^I$  is given in Algorithm 1 while the verification/decryption algorithm  $\mathcal{D}^I$  is given in Algorithm 2.

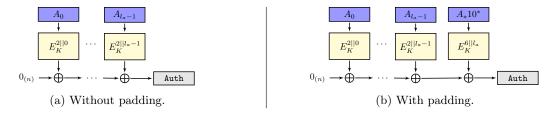

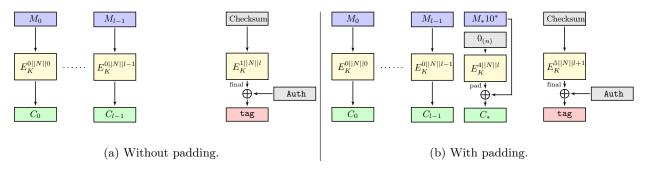

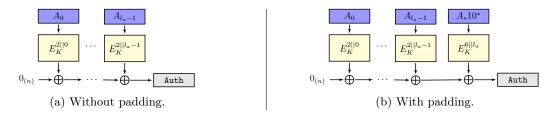

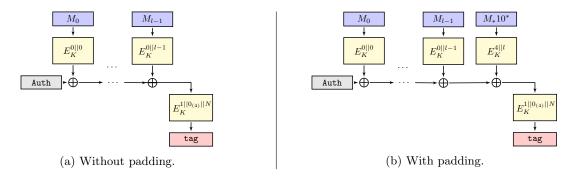

If the length of the associated data is not a multiple of the block size, the final block is padded with the 10\* padding, as depicted in Figure 2.1. The same applies for the message and the ciphertext as shown in Figures 2.2 and 2.3.

Figure 2.1: Handling of the associated data in the nonce-respecting mode.

Figure 2.2: Message processing for the nonce-respecting mode.

Figure 2.3: Ciphertext processing for the nonce-respecting mode.

## **Algorithm 1:** The encryption algorithm $\mathcal{E}_K^{\mathbf{I}}(N,A,M)$ .

In the tweak inputs, the value N is encoded on 120 bits, the integer values j and l are encoded on 68 bits, while the integer values i and  $l_a$  are encoded on 188 bits.

```

1 /* Associated data */

2 A_0 || \cdots || A_{l_a-1} || A_* \leftarrow A where each |A_i| = n and |A_*| < n

3 Auth \leftarrow 0_{(n)}

4 for i = 0 to l_a - 1 do

5 | Auth \leftarrow Auth \oplus E_K(0010||i,A_i)

6 end

7 if A_* \neq \epsilon then

8 Auth \leftarrow Auth \oplus E_K(0110||l_a, pad10^*(A_*))

9 end

/* Message */

11

12 M_0 || \cdots || M_{l-1} || M_* \leftarrow M where each |M_j| = n and |M_*| < n

13 Checksum \leftarrow 0_{(n)}

14 for j = 0 to l - 1 do

Checksum \leftarrow Checksum \oplus M_j

15

C_j \leftarrow E_K(0000||N||j,M_j)

16

17 end

18 if M_* = \epsilon then

Final \leftarrow E_K(0001||N||l, \text{ Checksum})

19

21 else

Checksum \leftarrow Checksum \oplus pad10^*(M_*)

22

Pad \leftarrow E_K(0100||N||l, 0_{(n)})

23

C_* \leftarrow M_* \oplus \lceil \operatorname{Pad} \rceil_{|M_*|}

\mathbf{24}

Final \leftarrow E_K(0101||N||l+1, \text{Checksum})

25

26

end

27

/* Tag generation */

29 tag \leftarrow Final \oplus Auth

30 return (C_0||\cdots||C_{l-1}||C_*, tag)

```

**Algorithm 2:** The verification/decryption algorithm  $\mathcal{D}_K^{\mathrm{I}}(N,A,C,\mathsf{tag})$ . In the tweak inputs, the value N is encoded on 120 bits, the integer values j and l are encoded on 68 bits, while the integer values i and  $l_a$  are encoded on 188 bits.

```

1 /* Associated data */

2 A_0 || \cdots || A_{l_a-1} || A_* \leftarrow A where each |A_i| = n and |A_*| < n

3 Auth \leftarrow 0_{(n)}

4 for i = 0 to l_a - 1 do

Auth \leftarrow Auth \oplus E_K(0010||i, A_i)

6 end

7 if A_* \neq \epsilon then

8 Auth \leftarrow Auth \oplus E_K(0110||l_a, pad10^*(A_*))

9 end

11 /* Ciphertext */

12 C_0 || \cdots || C_{l-1} || C_* \leftarrow C where each |C_j| = n and |C_*| < n

13 Checksum \leftarrow 0_{(n)}

14 for j = 0 to l - 1 do

M_j \leftarrow D_K(0000||N||j, C_j)

15

Checksum \leftarrow Checksum \oplus M_i

16

17 end

18 if C_* = \epsilon then

Final \leftarrow E_K(0001||N||l, \text{ Checksum})

19

20

21 else

Pad \leftarrow E_K(0100||N||l, 0_{(n)})

22

M_* \leftarrow C_* \oplus \lceil \operatorname{Pad} \rceil_{|C_*|}

23

Checksum \leftarrow Checksum \oplus pad10^*(M_*)

\mathbf{24}

Final \leftarrow E_K(0101||N||l+1, \text{Checksum})

25

26

end

27

/* Tag generation */

29 tag' \leftarrow Final \oplus Auth

30 if tag' = tag then

return (M_0||\cdots||M_{l-1}||M_*)

32 else

\mathbf{return} \perp

34 end

```

## 2.2.2 Nonce-Misuse Resistant Mode

This scheme is the variant of SCT introduced in Deoxys [33]: SCT-2. In this mode, the tweak length is 128 bits while the size of the nonce N remains unchanged and is 120 bits. The encryption algorithm  $\mathcal{E}^{II}$  is given in Algorithm 3 while the verification/decryption algorithm  $\mathcal{D}^{II}$  is given in Algorithm 4.

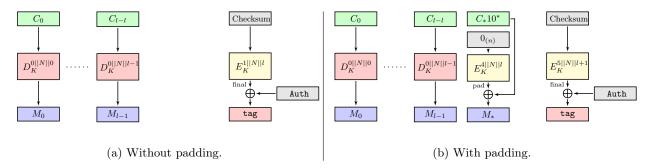

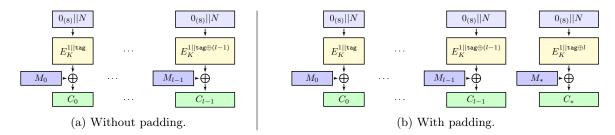

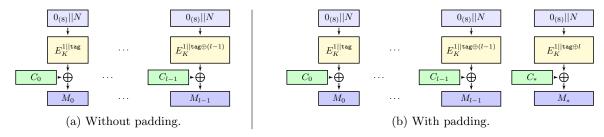

The associated data is processed as in the previous variant, as depicted in Figure 2.4. The processing of the message is shown in Figure 2.5 and 2.6 and decryption is shown in Figure 2.7.

Figure 2.4: Handling of the associated data in the nonce-misuse resistant mode.

Figure 2.5: Message processing in the authentication part of the nonce-misuse resistant mode.

Figure 2.6: Message processing in the encryption part of the nonce-misuse resistant mode.

Figure 2.7: Ciphertext processing in the decryption part of the nonce-misuse resistant mode.

## **Algorithm 3:** The encryption algorithm $\mathcal{E}_K^{\mathtt{II}}(N,A,M)$ .

In the tweak inputs, the integer values i, j, l and  $l_a$  are encoded on 124 bits. Moreover,  $tag \oplus j$  values are encoded on 127 bits (the most significant bit is truncated since  $|tag| = \tau$ ).

```

1 /* Associated data */

2 A_0 || \cdots || A_{l_a-1} || A_* \leftarrow A where each |A_i| = n and |A_*| < n

3 Auth \leftarrow 0_{(n)}

4 for i = 0 to l_a - 1 do

5 Auth \leftarrow Auth \oplus E_K(0010||i,A_i)

6 end

7 if A_* \neq \epsilon then

8 Auth \leftarrow Auth \oplus E_K(0110||l_a, pad10^*(A_*))

9 end

10

11 /* Message authentication and tag generation */

12 M_0 || \cdots || M_{l-1} || M_* \leftarrow M where each |M_j| = n and |M_*| < n

13 tag \leftarrow Auth

14 for j = 0 to l - 1 do

15 | tag \leftarrow tag \oplus E_K(0000||j,M_j)

16 end

17 if M_* \neq \epsilon then

18 |  tag \leftarrow tag \oplus E_K(0100||l,pad10^*(M_*))

19 end

20 tag \leftarrow E_K(0001||0^4||N, tag)

22 /* Message encryption */

23 for j = 0 to l - 1 do

24 C_j \leftarrow M_j \oplus E_K(1||\mathsf{tag} \oplus j, 0^8||N)

25 end

26 if M_* \neq \epsilon then

27 C_* \leftarrow M_* \oplus \lceil E_K(1||\mathsf{tag} \oplus l, 0^8||N) \rceil_{|M_*|}

28 else

29 C_* \leftarrow \epsilon

30 end

31

32 return (C_0||\cdots||C_{l-1}||C_*, \text{tag})

```

**Algorithm 4:** The verification/decryption algorithm  $\mathcal{D}_K^{\mathrm{II}}(N,A,C,\mathsf{tag})$ . In the tweak inputs, the integer values i,j,l and  $l_a$  are encoded on 124 bits. Moreover,  $\mathsf{tag} \oplus j$  values are encoded on 127 bits (the most significant bit is truncated since  $|\mathsf{tag}| = \tau$ ).

```

1 /* Message decryption */

2 |C_0| \cdots |C_{l-1}| |C_* \leftarrow C| where each |C_j| = n and |C_*| < n

3 for j = 0 to l - 1 do

4 | M_j \leftarrow C_j \oplus E_K(1||\text{tag} \oplus j, 0^8||N)

5 end

6 if C_* \neq \epsilon then

7 M_* \leftarrow C_* \oplus \lceil E_K(1||\mathsf{tag} \oplus l, 0^8||N) \rceil_{|C_*|}

s else

9 M_* \leftarrow \epsilon

10 end

11

12 /* Associated data */

13 A_0 || \cdots || A_{l_a-1} || A_* \leftarrow A where each |A_i| = n and |A_*| < n

14 Auth \leftarrow 0_{(n)}

15 for i = 0 to l_a - 1 do

16 | Auth \leftarrow Auth \oplus E_K(0010||i,A_i)

17 end

18 if A_* \neq \epsilon then

19 | Auth \leftarrow Auth \oplus E_K(0110||l_a, pad10^*(A_*))

22 /* Message authentication and tag generation */

23 M_0 || \cdots || M_{l-1} || M_* \leftarrow M where each |M_j| = n and |M_*| < n

\mathbf{24}\ \mathsf{tag'} \leftarrow \mathrm{Auth}

25 for j = 0 to l - 1 do

26 | tag' \leftarrow tag' \oplus E_K(0000||j, M_i)

27 end

28 if M_* \neq \epsilon then

29 | \operatorname{tag}' \leftarrow \operatorname{tag}' \oplus E_K(0100||l,pad10^*(M_*))

31 tag' \leftarrow E_K(0001||0^4||N, tag')

33 /* Tag verification */

34 if tag' = tag then

35 | return (M_0||\cdots||M_{l-1}||M_*)

36 else

37 return \perp

38 end

```

## 2.3 The Tweakable Block Cipher LILLIPUT-TBC

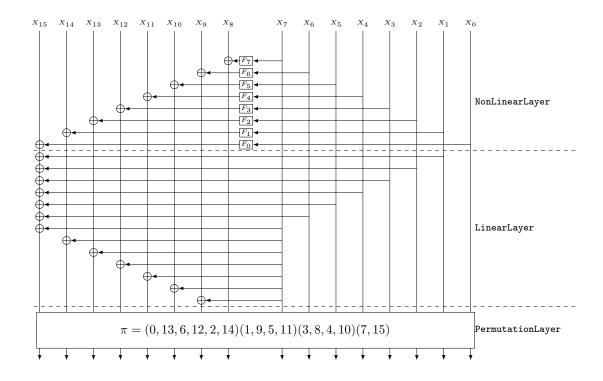

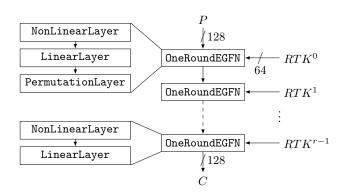

In this section we present our dedicated lightweight Tweakable Block Cipher LILLIPUT-TBC that is based on the EGFN [8] described in Fig. 2.8.

LILLIPUT-TBC is composed of 6 variants depending on the key lengths (possible key lengths are equal to 128, 192 and 256 bits) and on the tweak lengths (possible tweak lengths are equal to 128 or 192 bits). The different parameters for those variants are specified in Table 2.2. LILLIPUT-TBC-I for the three possible key lengths and a tweak length equal to 192 bits will be used in the mode LILLIPUT-I and LILLIPUT-TBC-II for the three possible key lengths and a tweak length equal to 128 bits will be used in the mode LILLIPUT-II.

| Name                | k   | t   | Nb of rounds $r$ |

|---------------------|-----|-----|------------------|

| LILLIPUT-TBC-I-128  | 128 | 192 | 32               |

| LILLIPUT-TBC-I-192  | 192 | 192 | 36               |

| LILLIPUT-TBC-I-256  | 256 | 192 | 42               |

| LILLIPUT-TBC-II-128 | 128 | 128 | 32               |

| LILLIPUT-TBC-II-192 | 192 | 128 | 36               |

| LILLIPUT-TBC-II-256 | 256 | 128 | 42               |

Table 2.2: Recommended parameter sets for LILLIPUT-TBC.

## 2.3.1 Encryption Process

LILLIPUT-TBC is a 128-bit tweakable block cipher with key sizes of 128, 192 or 256 bits and tweak sizes of 128 or 192 bits. The whole encryption process is depicted in Fig. 2.9. As previously explained, LILLIPUT-TBC uses an Extended Generalized Feistel Network (EGFN) with a 128-bit state and a round function acting at byte level. The state X is seen as 16 bytes, denoted  $X_{15}, \dots, X_0$ . In its 128-bit key version, the cipher is composed of r=32 rounds, i.e. 32 repetitions of a single EGFN called OneRoundEGFN, depicted in Fig. 2.8. Each  $F_j$  for j from 0 to 7 is defined as  $F_j = S(X_j \oplus RTK_j^i)$  where S is an S-box that acts at byte level and  $RTK_j^i$  is the byte of position j of the 64-bit subtweakey  $RTK^i$  of round i. The 32 64-bit subtweakeys  $RTK^i$  are generated from the master key and the tweak using the tweakey schedule.

In more details, the round function denoted OneRoundEGFN in Fig. 2.9 is composed of a layer of non linear components called NonLinearLayer for confusion; a new layer called LinearLayer in [8] that represent a linear layer made of linear components applied in a Feistel way; and a block-wise permutation called PermutationLayer for diffusion. All three layers act at byte level on the EGFN state X and together constitute one iteration of the EGFN, as shown in Fig. 2.8.

Note that with this new layer LinearLayer, it is possible to shuffle blocks better than what was possible using the block-wise permutation only of a classical Feistel scheme, while preserving the self-invertibility of the scheme.

Note that the last round skips the PermutationLayer for involution reasons.

For the 192-bit and 256-bit key versions, the number of rounds r is 36 and 42 respectively.

## Overview of the EGFN round function

The particular EGFN we use in LILLIPUT-TBC with k = 16 blocks is depicted in Fig. 2.8.

Figure 2.8: The EGFN used in LILLIPUT-TBC that reaches full diffusion in d=4 rounds. The permutation  $\pi$  is given as a product of cycles and can also be found in Table 2.3.

In more details, OneRoundEGFN is composed of:

- NonLinearLayer: It is the non-linear part of the EGFN and is made of 8 parallel updates of the EGFN state. Each  $F_j$  for j from 0 to 7 is defined as  $F_j = S(X_j \oplus RTK_j^i)$  where S is an S-box that acts at byte level given in Table 2.4 and  $RTK_j^i$  is the byte of position j of the 64-bit subtweakey  $RTK^i$  of round i.

- LinearLayer: It aims at providing quick diffusion between bytes and consists in xoring some bytes to some other bytes. More precisely, as depicted in Fig 2.8, blocks  $X_1$  to  $X_6$  are xored to block  $X_{15}$ , and block  $X_7$  is xored to blocks  $X_9$  to  $X_{15}$ .

- PermutationLayer: It consists in applying the permutation  $\pi$  given in Table 2.3 to the bytes.

## The permutation $\pi$ used in PermutationLayer

The permutation  $\pi$  is given in Table 2.3. It has been chosen to maximize the number of active S-boxes on 18, 19 and 20 rounds as it will be shown in Section 3.4. For each round  $i \in \{0, \cdots, r-1\}$ , let us denote  $Y^i$  the output at round i after the transformations NonLinearLayer and LinearLayer with  $Y^i = (Y^i_{15}, \cdots, Y^i_0)$  its byte representation, i.e.  $Y^i = (Y^i_{15}, \cdots, Y^i_0) = \text{LinearLayer}(\text{NonLinearLayer}(X^i))$ . Then, the PermutationLayer is applied on  $Y^i$  in the following way:

$$\forall i \in \{1, \cdots, r-2\}, \forall j \{0, \cdots, 15\} \in X_{\pi(j)}^i = Y_j^{i-1}.$$

Table 2.3: Block permutation  $\pi$  used in encryption mode and its inverse  $\pi^{-1}$  used in decryption mode.

|           | i          | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|-----------|------------|----|----|----|----|----|----|----|----|---|---|----|----|----|----|----|----|

| 7         | $\tau(i)$  | 13 | 9  | 14 | 8  | 10 | 11 | 12 | 15 | 4 | 5 | 3  | 1  | 2  | 6  | 0  | 7  |

| $\pi^{-}$ | $^{-1}(i)$ | 14 | 11 | 12 | 10 | 8  | 9  | 13 | 15 | 3 | 1 | 4  | 5  | 6  | 0  | 2  | 7  |

## The S-box S used in NonLinearLayer

The S-box S used in NonLinearLayer is the 8-bit S-box given in Table 2.4. The properties of this S-box will be described in Section 3.2.3 of the Chapter 3.

|    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 00 | 20 | 00 | B2 | 85 | 3B | 35 | A6 | A4 | 30 | E4 | 6A | 2C | FF | 59 | E2 | 0E |

| 10 | F8 | 1E | 7A | 80 | 15 | BD | 3E | B1 | E8 | F3 | A2 | C2 | DA | 51 | 2A | 10 |

| 20 | 21 | 01 | 23 | 78 | 5C | 24 | 27 | B5 | 37 | C7 | 2B | 1F | AE | 0A | 77 | 5F |

| 30 | 6F | 09 | 9D | 81 | 04 | 5A | 29 | DC | 39 | 9C | 05 | 57 | 97 | 74 | 79 | 17 |

| 40 | 44 | C6 | E6 | E9 | DD | 41 | F2 | 8A | 54 | CA | 6E | 4A | E1 | AD | B6 | 88 |

| 50 | 1C | 98 | 7E | CE | 63 | 49 | 3A | 5D | 0C | EF | F6 | 34 | 56 | 25 | 2E | D6 |

| 60 | 67 | 75 | 55 | 76 | В8 | D2 | 61 | D9 | 71 | 8B | CD | 0B | 72 | 6C | 31 | 4B |

| 70 | 69 | FD | 7B | 6D | 60 | 3C | 2F | 62 | 3F | 22 | 73 | 13 | C9 | 82 | 7F | 53 |

| 80 | 32 | 12 | A0 | 7C | 02 | 87 | 84 | 86 | 93 | 4E | 68 | 46 | 8D | C3 | DB | EC |

| 90 | 9B | В7 | 89 | 92 | A7 | BE | 3D | D8 | EA | 50 | 91 | F1 | 33 | 38 | E0 | A9 |

| A0 | A3 | 83 | A1 | 1B | CF | 06 | 95 | 07 | 9E | ED | В9 | F5 | 4C | C0 | F4 | 2D |

| В0 | 16 | FA | B4 | 03 | 26 | В3 | 90 | 4F | AB | 65 | FC | FE | 14 | F7 | E3 | 94 |

| C0 | EE | AC | 8C | 1A | DE | СВ | 28 | 40 | 7D | C8 | C4 | 48 | 6B | DF | A5 | 52 |

| D0 | E5 | FB | D7 | 64 | F9 | F0 | D3 | 5E | 66 | 96 | 8F | 1D | 45 | 36 | CC | C5 |

| E0 | 4D | 9F | BF | 0F | D1 | 08 | EB | 43 | 42 | 19 | E7 | 99 | A8 | 8E | 58 | C1 |

| F0 | 9A | D4 | 18 | 47 | AA | AF | BC | 5B | D5 | 11 | D0 | В0 | 70 | BB | 0D | BA |

Table 2.4: The S-box in hexadecimal notation. The column indicates the least significant nibble and the row indicates the most significant nibble of the S-box input.

## Overall encryption process

Fig. 2.9 gives an overview of the complete encryption process of LILLIPUT-TBC for all its variants.

Figure 2.9: LILLIPUT-TBC Encryption process.

## 2.3.2 Decryption Process

As LILLIPUT-TBC is a Feistel network, decryption is quite analogous to encryption but uses the inverse block permutation  $\pi^{-1}$  given in Table 2.3 and the subkeys in the reverse order. Note that the tweakey process could be inverted at low cost.

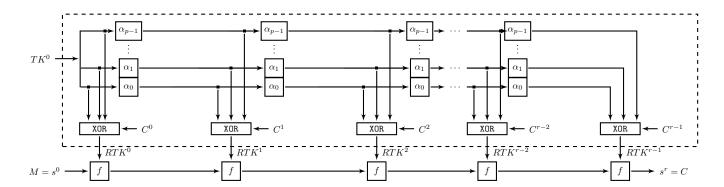

## 2.3.3 Tweakey Schedule

An adapted version of the TWEAKEY framework [32] was used as a building block for the scheduling of the key and the tweak. More specifically, we used a variant of the STK construction, where the key and the tweak inputs are handled almost the same way. The proposed version is depicted in Fig. 2.10.

Figure 2.10: The tweakey schedule. f represents the round function OneRoundEGFN.

The tweakey schedule produces the r=32 (36 or 42 respectively) 64-bit subtweakeys  $RTK^0$  to  $RTK^{r-1}$  from the 128-bit (192 or 256 respectively) master key K and the tweak T that is 128 bits long when LILLIPUT-TBC-II is used and 192 bits long tweak when LILLIPUT-TBC-I is used.

As done in the STK construction, at each round  $i \in \{0, \dots, r-1\}$ , the inner state  $TK^i$  is divided into p = (t+k)/64 lanes that we denote  $TK^i_j$ ,  $j \in \{0, \dots, p-1\}$ , where k is the key length and t is the tweak length. The values of p are shown in Table 2.5, depending on which version of LILLIPUT-TBC is used.

| Name                | k   | t   | p | r  |

|---------------------|-----|-----|---|----|

| LILLIPUT-TBC-I-128  | 128 | 192 | 5 | 32 |

| LILLIPUT-TBC-I-192  | 192 | 192 | 6 | 36 |

| LILLIPUT-TBC-I-256  | 256 | 192 | 7 | 42 |

| LILLIPUT-TBC-II-128 | 128 | 128 | 4 | 32 |

| LILLIPUT-TBC-II-192 | 192 | 128 | 5 | 36 |

| LILLIPUT-TBC-II-256 | 256 | 128 | 6 | 42 |

Table 2.5: Recommended parameter sets for LILLIPUT-TBC and associated number of tweakey lanes.

$TK^0$  is initialized with the concatenation of the tweak T and the master key K. The first 2 (or 3) lanes are thus dedicated to the 128-bit (or 192-bit) tweak. The key is then stored in the following 2, 3 or 4 lanes, depending on its size.

For each round i, the 8-byte subtweakey word that is produced is denoted  $RTK^{i}$ :

$$\forall i \in \{0, \cdots, r-1\}, \quad RTK^i = RTK_7^i ||RTK_6^i||RTK_5^i||RTK_4^i||RTK_3^i||RTK_2^i||RTK_1^i||RTK_0^i|$$

where  $RTK_j^i$  is the byte that is xored to block  $X_j$  then used as an input of the nonlinear function  $F_j$  in the LILLIPUT-TBC round function of the encryption process.

The subtweakey word is obtained by xoring all p  $TK_j^i$  lanes and a round-dependent constant denoted  $C^i$  together. In our proposal, the round constant  $C^i$  is simply the round number i:

$$\forall i \in \{0, \cdots, r-1\}, \quad RTK^i = \bigoplus_{j=0}^{p-1} TK_j^i \oplus i.$$

To update the tweakey, at each round  $i \in \{1, \dots, r-1\}$ , each 64-bit lane  $TK_j^i$  is multiplied by a nonzero coefficient denoted  $\alpha_j$ , with  $j \in \{0, \dots, p-1\}$ . The first coefficient  $\alpha_0$  is set to 1 and corresponds

to the identity function. The other coefficients were carefully chosen such that in r consecutive rounds, at most (p-1) cancellations occur as will be shown in Section 3.2. Next, we describe how to generate the sequences induced by coefficients  $\alpha_j$   $(j=1,\cdots,6)$ .

### Sequences

The  $\alpha$ -multiplications are computed using word-ring-LFSRs [7]. The sequences constructed as  $\alpha$ -multiplications for the tweakey on  $GF(2^{64})$  using word-ring-LFSRs are the following ones: consider first a 64-bit lane in byte notation as  $x=(x_7,\cdots,x_0)$  where  $x_7$  is the most significant byte and  $x_0$  is the least significant one. In binary notations, we obtain the following vector of 64 bits:  $x=(x_{63}^b,\cdots,x_0^b)$ . Thus, we have,  $\alpha_0=I$ , where I is the  $64\times 64$  identity matrix,  $\alpha_1=M$ ,  $\alpha_2=M^2$ ,  $\alpha_3=M^3$ ,  $\alpha_4=M_R$ ,  $\alpha_5=M_R^2$  and  $\alpha_6=M_R^3$ .

Then the sequence generated by  $\alpha_1$  is produced using the ring-LFSR represented at byte level word by the following matrix:

$$M = \begin{pmatrix} 0 & Id & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & Id & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & S^{\leqslant 3} & Id & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & S^{\gg 3} & Id & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & Id & 0 & 0 \\ 0 & S^{\leqslant 2} & 0 & 0 & 0 & 0 & Id & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & Id \\ Id & 0 & 0 & 0 & 0 & 0 & 0 & 0 \end{pmatrix}$$

where Id is the  $8\times 8$  identity matrix. The primitive polynomial associated with this matrix is computed as  $Det(I-M\cdot X)$  at binary level, which gives:  $x^{64}+x^{58}+x^{42}+x^{40}+x^{35}+x^{34}+x^{29}+x^{26}+x^{24}+x^{23}+x^{19}+x^{19}+1$ . The multiplication by  $\alpha_1$  is then generated as  $(y_7,\cdots,y_0)^t=M\cdot(x_7,\cdots,x_0)^t$ . Thus, we have:  $(y_7,\cdots,y_0)^t=(x_6,x_5,x_4\oplus x_5\ll 3,x_3\oplus x_4\gg 3,x_2,x_1\oplus x_6\ll 2,x_0,x_7)^t$ .

$$M^{2} = \begin{pmatrix} 0 & 0 & Id & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & S^{\ll 3} & Id & 0 & 0 & 0 & 0 \\ 0 & 0 & S^{\ll 6} & M_{1} & Id & 0 & 0 & 0 \\ 0 & 0 & 0 & S^{\gg 6} & S^{\gg 3} & Id & 0 & 0 \\ 0 & S^{\ll 2} & 0 & 0 & 0 & 0 & Id & 0 \\ 0 & 0 & S^{\ll 2} & 0 & 0 & 0 & 0 & Id \\ Id & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & Id & 0 & 0 & 0 & 0 & 0 & 0 \end{pmatrix}$$

with  $M_1$  equal to the binary  $8 \times 8$  following matrix:

$$\begin{pmatrix} 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \end{pmatrix}$$

and

$$M^{3} = \begin{pmatrix} 0 & 0 & S^{\ll 3} & Id & 0 & 0 & 0 & 0 \\ 0 & 0 & S^{\ll 6} & M_{1} & Id & 0 & 0 & 0 \\ 0 & 0 & 0 & M_{2} & M_{1} & Id & 0 & 0 \\ 0 & S^{\ll 2} & 0 & 0 & S^{\gg 6} & S^{\gg 3} & Id & 0 \\ 0 & 0 & S^{\ll 2} & 0 & 0 & 0 & 0 & Id \\ Id & 0 & S^{\ll 5} & S^{\ll 2} & 0 & 0 & 0 & 0 \\ 0 & Id & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & Id & 0 & 0 & 0 & 0 & 0 \end{pmatrix}$$

with  $M_2$  a binary matrix of size  $8 \times 8$  equal to

To generate the three following sequences, we use the following matrices using the reciprocal primitive polynomial of  $x^{64} + x^{58} + x^{42} + x^{40} + x^{35} + x^{34} + x^{29} + x^{26} + x^{24} + x^{23} + x^{19} + x^{10} + 1$  equal to  $x^{64} + x^{54} + x^{45} + x^{41} + x^{40} + x^{38} + x^{35} + x^{30} + x^{29} + x^{24} + x^{22} + x^6 + 1$ .

The outputs are then computed in the reverse order using the relation  $(y_0, \dots, y_7)^t = M_R \cdot (x_0, \dots, x_7)^t$ . Note that the associated binary words are also written in the opposite way compared with the computations performed for M,  $M^2$  and  $M^3$ . It means that, in this case, at binary level, we have  $x = (x_0^b, \dots, x_{63}^b)$ and  $x_i = (x_{8\cdot i+0}^b, \cdots, x_{8\cdot i+7}^b)$ . Thus, we have:  $(y_0, \cdots, y_7)^t = (x_1, x_2, x_3 \oplus x_4 \ll 3, x_4, x_5 \oplus x_6 \gg 3, x_6 \oplus x_3 \gg 2, x_7, x_0)^t$ .

$$M_R = \begin{pmatrix} 0 & Id & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & Id & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & Id & S^{\ll 3} & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & Id & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & Id & S^{\gg 3} & 0 \\ 0 & 0 & 0 & S^{\gg 2} & 0 & 0 & Id & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & Id \\ Id & 0 & 0 & 0 & 0 & 0 & 0 & 0 \end{pmatrix}$$

with  $M_3$  a binary matrix of size  $8 \times 8$  equal to

and

$$M_R^3 = \begin{pmatrix} 0 & 0 & 0 & Id & S^{\ll 3} & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & Id & S^{\ll 3} & M_3 & 0 \\ 0 & 0 & 0 & M_4 & 0 & Id & M_1 & M_3 \\ 0 & 0 & 0 & S^{\gg 2} & 0 & 0 & Id & S^{\gg 3} \\ S^{\gg 3} & 0 & 0 & 0 & S^{\gg 2} & 0 & 0 & Id \\ Id & 0 & 0 & 0 & 0 & S^{\gg 2} & S^{\gg 5} & 0 \\ 0 & Id & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & Id & 0 & 0 & 0 & 0 & 0 \end{pmatrix}$$

with  $M_4$  is a binary matrix of size  $8 \times 8$  equal to

The periods of each sequence given by the word-ring-LFSRs produced by the previous matrices are respectively:  $2^{64} - 1$  for the sequences produced using M,  $M^2$ ,  $M_R$ ,  $M_R^2$  and  $\frac{2^{64} - 1}{3}$  for the sequences produced using  $M^3$  and  $M_R^3$ .

# Chapter 3

# Design Rationale and Security Analysis

In this chapter, we will detail the design choices we made for LILLIPUT-TBC and we provide a complete security analysis regarding a wide variety of attacks.

## 3.1 Design Rationale of the Modes of Operation

## 3.1.1 ⊖CB3

The OCB mode (Offset Codebook Mode) was designed by Phillip Rogaway, who took inspiration from Charanjit Jutla's IAPM (Integrity Aware Parallelizable Mode) [35]. The original authenticated-encryption scheme has then been refined several times, leading to three named versions: OCB1 [49], OCB2 [48] and OCB3 [39]. The main change introduced with OCB2 is the possibility to handle Associated Data (AD), while the modifications made in OCB3 are rather minor (mostly a change in the way offsets are incremented). The OCB mode has many advantages, starting with the fact that it is parallelizable and only requires one block cipher invocation per message block, in contrary to schemes like GCM. In [39], Krovetz and Rogaway also introduced a tweakable block cipher generalization of OCB3 denoted ΘCB3, which is at the source of the mode used for our candidate LILLIPUT-I.

OCB is covered by the United States Patent No. 7,949,129, United States Patent No. 8,321,675, United States Patent No. 7,046,802 and United States Patent No. 7,200,22. Still, it is unclear if OCB3 is also covered by patents. This lack of clarity is part of the reason why we selected LILLIPUT-II to be our primary member.

Under the assumption that the underlying (tweakable) block cipher is secure as a strong-PRP (PseudoRandom Permutation), OCB is provably secure and achieves confidentiality and authenticity. Confidentiality means that an adversary cannot make the distinction between OCB outputs and random bits, while authenticity (of ciphertexts) means that she cannot produce a valid nonce-ciphertext pair (different from the ones she previously obtained). Note that the various variants of OCB are not designed to resist to nonce reuse nor to enjoy beyond-birthday-bound security.

## 3.1.2 SCT-2

The Synthetic Counter in Tweak mode (SCT) was first devised at Crypto 2016 by Thomas Peyrin and Yannick Seurin [44]. Few months later, the mode was slightly modified by the same authors associated with Jérémy Jean and Ivica Nikolic to be used as a mode for one of the member of the family of authenticated ciphers Deoxys v1. 41 [33], their submission to CAESAR (Competition for Authenticated Encryption: Security, Applicability, and Robustness). The rearranged mode was named SCT-2, and the corresponding authenticated cipher was coined Deoxys-II.

The difference between SCT and SCT-2 only lies in the way the tag is produced (the encryption part is similar), a change that was done "in order to provide graceful degradation of security for authentication with the maximal number of repetitions of nonce" [33].

#### 3.2 Design Rationale of Lilliput-TBC

When designing Lilliput-TBC from the block cipher Lilliput, our overall goal was to maximize diffusion between nibbles or bytes while keeping reasonable implementation performances. This diffusion could be measured using the notion of full diffusion delay of [8]. It will be denoted by d and corresponds to the minimum number of rounds needed for all output bytes or nibbles to depend on all input bytes or nibbles. It is closely related to some structural attacks such as impossible differentials or integral attacks, as shown in [57, 8].

We decided to use the EGFN inferred in LILLIPUT [6] to reach this purpose because the full diffusion delay of the EGFN of LILLIPUT is equal to d=4 which is the best diffusion delay obtained for a

We chose a 128-bit state as it is consistent with the NIST requirements. We split that state into 16 bytes so that the block size matches the S-box size, i.e. the non-linear layer is made only of 8 parallel calls to an 8-bit S-box and 8 subkey additions. As said before, the  $\pi$  permutation has been chosen to maximize the number of active S-boxes on 18, 19 and 20 rounds (see Section 3.4 and Table 3.2 for more details).

From those results and the security analysis performed in Section 3.4 and summed up in Table 3.5, we also deduced the number of rounds of each instance of LILLIPUT-I and of LILLIPUT-II equal to 32, 36 or 42 rounds.

#### 3.2.1The EGFN Structure

As done in [57, 8], we analyze here the security of our underlying EGFN scheme regarding the pseudorandomness of the scheme. Note that the pseudorandomness bounds obtained are generic and essentially depend on the d value. We thus introduce the pseudo-random-permutation advantage (prp-advantage) and the strong-pseudo-random-permutation advantage (sprp-advantage) of an adversary. For this purpose, we introduce the two advantage notations as:

$$Adv_{\mathsf{C}}^{\mathsf{prp}}(q) = \max_{\mathsf{A}: r \in \mathsf{CPA}} \left| \Pr[\mathsf{A}^{\mathsf{C}} = 1] - \Pr[\mathsf{A}^{\mathsf{P}_n} = 1] \right| \tag{3.1}$$

$$Adv_{C}^{\mathsf{prp}}(q) = \max_{A:q\text{-}\mathsf{CPA}} \left| \Pr[A^{\mathsf{C}} = 1] - \Pr[A^{\mathsf{P}_n} = 1] \right|$$

$$Adv_{C}^{\mathsf{sprp}}(q) = \max_{A:q\text{-}\mathsf{CCA}} \left| \Pr[A^{\mathsf{C},\mathsf{C}^{-1}} = 1] - \Pr[A^{\mathsf{P}_n,\mathsf{P}_n^{-1}} = 1] \right|$$

$$(3.1)$$

where C is the encryption function of an n-bit block cipher composed of Uniform Random Functions (URFs) as internal modules whereas  $C^{-1}$  is its inverse;  $P_n$  is an n-bit Uniform Random Permutation (URP) uniformly distributed among all the *n*-bit permutations;  $P_n^{-1}$  is its inverse. The adversary, A, tries to distinguish C from  $P_n$  using q queries in a CPA (Chosen Plaintext Attack) and tries to distinguish, always using q queries,  $(C, C^{-1})$  from  $(P_n, P_n^{-1})$  in a CCA (Chosen Ciphertext Attack). The notation means that the final guess of the adversary A is either 0 if A thinks that the computations are done using  $P_n$ , or 1 if A thinks that the computations are done using C. The maximums of Equations (3.1,3.2) are taken over all possible adversaries A with q queries and an unbounded computational power.

To prove the bounds of our scheme in those models, we recall the result proved in [6]: let  $\Phi_{kc,r}$  denote our k-block scheme acting on c-bit blocks with n = kc, using r rounds and with diffusion delay d. We then have (the proof can be found in [6]):

**Theorem 1** Given the r-round EGFN  $\Phi_{kc,r}$  with k branches acting on c-bit blocks with a diffusion delay d where all c-bit round functions are independent URFs. Then we have:

$$Adv_{\Phi_{kc,d+2}}^{\mathsf{prp}}(q) \leq \frac{kd}{2^c}q^2 \tag{3.3}$$

$$\operatorname{Adv}_{\Phi_{kc,d+2}}^{\mathsf{prp}}(q) \leq \frac{kd}{2^{c}}q^{2} \tag{3.3}$$

$$\operatorname{Adv}_{\Phi_{kc,2d+2}}^{\mathsf{sprp}}(q) \leq \frac{kd}{2^{c-1}}q^{2} \tag{3.4}$$

Thus, we have a classical security proof for the choice of the underlying EGFN used in LILLIPUT-TBC. Note that, in our case, c is equal to 8.

## 3.2.2 The $\pi$ Permutation

Full diffusion delay is closely related to some structural attacks such as impossible differentials or integral attacks, as shown in [57, 8]. As there are many EGFNs that achieve d = 4, we chose one by taking other considerations into account. Specifically, we chose the block-wise permutation to maximize resistance against differential and linear cryptanalysis.

We identified the criterion for a permutation  $\pi$  to achieve d=4 to be as follows: first,  $\pi$  must swap the 8 right-most blocks with the 8 left-most, and second,  $\pi$  must specifically swap blocks  $Y_7$  and  $Y_{15}$  (a complete proof could be found in [8, 6]).

Up to block reindexing equivalence, there are exactly 37108 such permutations. For each of them, we computed the minimal number of differentially and linearly active S-boxes up to 20 rounds (see Section 3.4.1 and Table 3.2 for more details) and picked the one that maximizes the number of active S-boxes on 18, 19 and 20 rounds.

### 3.2.3 The S-box

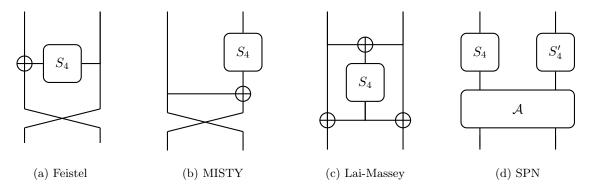

### Overall structure

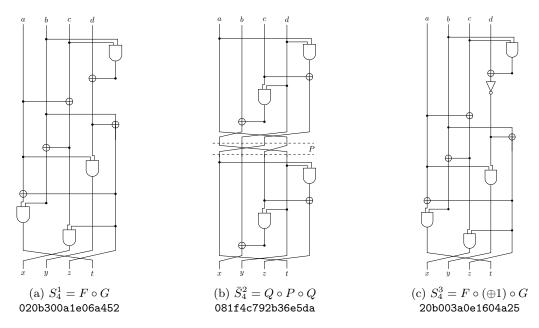

We chose to build the 8-bit S-box from smaller ones so that it could be implemented with a fewer number of gates, which is a valuable property for hardware and bit-sliced software implementations. S-boxes built in this fashion usually rely on one of the four constructions depicted in Fig 3.1. We defined the following

Figure 3.1: Some structures to build 2n-bit S-boxes from n-bit ones.

selection criteria for the candidate S-box:

- Differential uniformity  $\delta \leq 10$

- Linearity  $\mathcal{L} \leq 64$

- Algebraic degree  $\mathsf{deg} \geq 6$  .

All constructions discussed above need to be iterated several times in order to achieve the desired cryptographic properties. Regarding Feistel and MISTY networks, [17] gives lower bounds on the differential uniformity and linearity for 3-round balanced constructions. In this case, Feistel networks provide better cryptographic properties as it is possible to reach  $\delta=8$  and  $\mathcal{L}=64$  versus  $\delta=16$  and  $\mathcal{L}=64$  for MISTY networks. It comes from the fact that Feistel networks do not require inner 4-bit S-boxes to be permutations, allowing the use of Almost Perfect Nonlinear (APN) functions as inner components. Still, it has been shown that 3-round unbalanced MISTY networks (e.g., dividing the 8-bit input into two inequal parts of 3 and 5 bits) can be used to build 8-bit S-boxes with  $\delta=8$  [17]. However, because the unbalanced words induce components with strong unbalanced degrees for the ANF, we decided to rule out this option.

Regarding the Lai-Massey scheme, the family of block ciphers FOX [34] uses a 3-round iterated structure in order to build an 8-bit S-box with  $\delta=16$  and  $\mathcal{L}=64$ . On the other side, some cryptographic primitives simply add a nonlinear layer (i.e. two 4-bit S-boxes in parallel) at the beginning and/or at the end of the original scheme depicted in Fig. 3.1c instead of using an iterated structure and therefore save some XOR gates. For instance, the block cipher FLY [36] adds a nonlinear layer at the end of the scheme

while the hash function Whirlpool [3] also adds one at the beginning resulting in a total of three and five inner 4-bit S-boxes, respectively. As for the MISTY ladder, the Lai-Massey structure requires inner 4-bit S-boxes to be permutations and therefore constructions that use three 4-bit S-boxes cannot reach a differential uniformity as good as Feistel networks. Although the cryptographic properties achieved by the variant using five 4-bit S-boxes are compliant with our selection criteria (i.e.  $\delta = 8$ ,  $\mathcal{L} = 56$  and deg = 7 for the Whirlpool S-box), it is not worth the implementation cost.

The same reasoning can be applied to SPNs. For instance, the block cipher CLEFIA [55] uses two different 8-bit S-boxes and one of them relies on an SPN structure as defined in Fig. 3.1d with an additional nonlinear layer after  $\mathcal{A}$  which refers to a matrix multiplication over  $\mathbb{F}_{16}$ . It results in an S-box with  $\delta = 10$ ,  $\mathcal{L} = 56$  and  $\deg = 6$  which is compliant with our selection criteria. However, because it uses four 4-bit S-boxes, it is more heavy than a 3-round Feistel network to implement.

For all these reasons, we opted for an 8-bit S-box based on a 3-round balanced Feistel network. In the rest of this section,  $S_4^i$  refers to the inner 4-bit S-box at the *i*-th round.

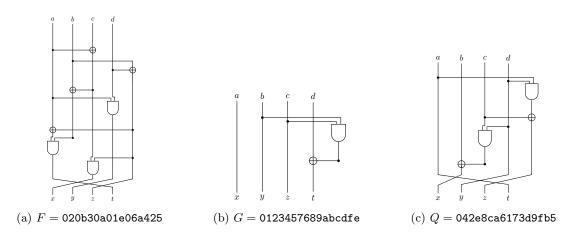

### Inner 4-bit S-boxes

According to [17], in order to reach  $\delta=8,\,S_4^1$  and  $S_4^3$  have to be APN functions while  $S_4^2$  has to be a permutation with differential uniformity 4. The authenticated block cipher SCREAM [26] uses an 8-bit S-box built in this manner where the underlying APN functions are  $S_4^1=020b300a1e06a452$  and  $S_4^3=20b003a0e1604a25$  and the permutation is  $S_4^2=02c75fd64e8931ba$ .

$S_4^1$  can be implemented using 11 instructions in total (either AND or OR or XOR or NOT or MOV), including 4 non-linear ones, while  $S_4^3$  is directly derived from it by adding a NOT instruction in order to avoid fixed points. Although it is possible to find APN functions over  $\mathbb{F}_{16}$  that are built using 10 instructions from the same instruction set, they all require at least 6 non-linear ones [17] which is not optimal regarding masked implementations.  $S_4^2$  is built using 9 instructions from the same instruction set, including 4 non-linear ones, which is the smallest implementation cost for a 4-bit S-box with differential uniformity 4 [60]. Therefore, the SCREAM S-box allows very efficient implementations with and without masking as it only requires 44 instructions in total including 12 non-linear ones.

However, the number of non-linear operations is not the only criteria regarding Threshold Implementations (TI) where an S-box with algebraic degree d requires at least n=d+1 shares. In order to limit the number of shares for a 4-bit S-box with d>2, it has been proposed to use its decomposition into quadratic bijections [43] (i.e.  $S_4^i = F \circ G$ ) so that it is possible to achieve a TI with n=3. In order to fulfill the uniformity criteria, it has been proposed to find affine functions  $A_1$  and  $A_2$  such that  $F = A_1 \circ \mathcal{Q} \circ A_2$ , so that when it is possible to achieve a uniform sharing of the quadratic function Q, applying  $A_1$  and  $A_2$  on all input and output shares respectively gives a uniform sharing of F [11].

In [15] the authors study first-order TIs for several 8-bit S-boxes, including the one used in SCREAM. It results that the two APN functions  $S_4^1$  and  $S_4^3$  can be directly decomposed into two quadratic functions while the permutation  $S_4^2$  requires affine functions as described above. In order to achieve more efficient TIs by saving the implemention cost of the affine functions, we looked for (and found) alternatives to  $S_4^2$  that could be directly decomposed into two quadratic functions.

We chose to investigate all possible circuits with a Breadth-First Search (BFS) approach, including only AND, XOR and NOT gates as they can be straightforwardly thresholded. This approach is very similar to [60]. We optimized the number of gates used without considering MOV instructions as we consider that wiring is free compared to the cost of the gates. We allowed 5 registers during the exploration. Keeping the affine equivalence notion of the previous paper, stopping the exploration to 8 gates allowed us to reach 62 affine equivalence classes, including 3 optimal classes according to [50]. Following the same notation as [11] to refer to the equivalence classes, the three optimal classes we reached are  $C_{223}$ ,  $C_{296}$  and  $C_{297}$ .

We focused on permutations of the optimal classes as they are the only ones with differential uniformity equal to 4. First, we eliminated candidates that did not allow to reach the selection criteria for the 8-bit S-box when used as  $S_4^2$  in a 3-round Feistel network. After this step, there were still candidates in each optimal class. In order to go further into the optimization of TIs, we investigated the decomposition of the remaining candidates. Following [11], we decomposed those cubic permutations into two quadratic functions. There are six quadratic classes denoted by  $Q_4$ ,  $Q_{12}$ ,  $Q_{293}$ ,  $Q_{294}$ ,  $Q_{299}$  and  $Q_{300}$ . It results

from our BFS exploration that these classes can be implemented with a minimum of 2, 4, 6, 4, 6 and 6 gates, respectively. Among these classes, only  $Q_4$ ,  $Q_{294}$  and  $Q_{299}$  contain permutations that are uniform using direct sharing. However, neither  $C_{223}$  nor  $C_{296}$  nor  $C_{297}$  can be decomposed using  $Q_4$ . On the other hand, because only  $C_{223}$  can be decomposed into two quadratic functions of the class  $Q_{294}$  that are uniform using direct sharing, this makes  $C_{223}$  the most interesting optimal class we reached regarding TIs.

As stated before, contrary to  $S_4^2$ , our aim was to avoid linear permutations between the quadratic functions. As we consider that wire permutations  $\omega_i$  are free, for all the remaining candidates C in  $C_{223}$ , we looked for 4-gate circuits  $Q_i$  and  $Q_j$  of  $Q_{294}$  that are uniform using direct sharing, such that  $C = \omega_1 \circ Q_i \circ \omega_2 \circ Q_j \circ \omega_3$ . As a final step to determine which composition to use, we calculated the cost (considered in Gate Equivalents – GEs) of a 3-share TI of all of them using this formula:

$$GE = 3GE_X \cdot X + (6GE_X + 9GE_A) \cdot A + GE_N \cdot N \tag{3.5}$$

with  $GE_X$  the area and X the number of XOR gates,  $GE_A$  the area and A the number of AND gates and  $GE_N$  the area and N the number of NOT gates. It comes from the fact that, when considering 3-share TIs, thresholding an XOR gate requires 3 XOR gates while thresholding an AND gate requires 6 XOR and 9 AND gates. Taking  $GE_X = \frac{8}{3}$ ,  $GE_A = \frac{4}{3}$  and  $GE_N = \frac{2}{3}$ , we found the minimum at  $72 \cdot 2 = 144GE_S$ . Note that it does not include the cost of registers between the two permutations that are needed to ensure security against glitches.

Among the several compositions that can be implemented using 144GEs, we chose the permutation illustrated in Fig. 3.3b as it constitutes the only candidate that results from the composition of the same quadratic permutation Q = 042e8ca6173d9fb5, allowing to optimize the area cost in particular cases.

Figure 3.2: Quadatric functions used to build the cubic 4-bit S-boxes.

To put it in a nutshell, our 8-bit S-box is obtained by combining the two APN functions from the SCREAM S-box with the 4-bit permutation  $\bar{S}_4^2 = 081f4c792b36e5da$  in a 3-round Feistel network and achieves  $\delta = 8$ ,  $\mathcal{L} = 64$  and  $\deg = 6$  without fixed points. Thanks to the BFS exploration, we ensure that our S-box requires a small number of gates and that its TI is efficient as it uses the smallest circuits of its possible decompositions and futhermore, it does not require the use of affine permutations when decomposed into two quadratic functions. The 4-bit S-boxes are depicted in Fig. 3.3 while the underlying quadratic functions are depicted in Fig. 3.2, where a and d refer to the most and the least significant bits, respectively.

Figure 3.3: The three inner 4-bit S-boxes.

## 3.2.4 The Tweakey Schedule

As done for some other Tweakable Block Ciphers, we first looked at the TWEAKEY construction of [32] that fills p lanes of n bits divided into m words of c bits with the concatenation of the tweak T and of the key K. Then, to produce the subtweakey of each round, the TWEAKEY framework applies, on each lane, a permutation h acting on the m words and then multiply each of the m elements of c bits by a primitive root  $\alpha_i, \forall i \in \{0, \dots, p-1\}$  over  $GF(2^c)$  different for each lane. Then, the subtweakey is the XOR of the p lanes and of a constant. From this construction that could be seen as the tensorial product of m Vandermonde matrices, the authors could deduce that the number of cancellations on r+1 subtweakeys is at most equal to (p-1). Indeed, the updating function (excluding the p permutation) for the p bits words could be written as the following Vandermonde matrix

$$V = \begin{pmatrix} \alpha_0^0 & \alpha_0^1 & \alpha_0^2 & \cdots & \alpha_0^r \\ \alpha_1^0 & \alpha_1^1 & \alpha_1^2 & \cdots & \alpha_1^r \\ \alpha_2^0 & \alpha_2^1 & \alpha_2^2 & \cdots & \alpha_2^r \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ \alpha_{p-1}^0 & \alpha_{p-1}^1 & \alpha_{p-1}^2 & \cdots & \alpha_{p-1}^r \end{pmatrix}$$

when all  $\alpha_i$  with  $0 \le i \le r$  are distinct considering that  $r < ord(\alpha)$ . In this case, the code defined by V is a Reed-Solomon code of length r+1 and dimension p over  $GF(2^c)$  and it is known to be MDS (Maximum Distance Separable). It means that its minimum distance is equal to r+1-(p+1).

For designing our own tweakey schedule, we adopted the same idea to keep the Vandermonde strategy in order to guarantee the maximal possible number of cancellations. However, as we wanted to reduce the latency of the tweakey schedule and thus the number of computations, we adopted the following strategy instead of considering a lane as a vector of m elements of  $GF(2^c)$ : We directly consider the field  $GF(2^{cm})$  that will be equal in our case to  $GF(2^{64})$ . Indeed, in our case, the size of each lane is equal to  $\frac{n}{2} = 64$  bits due to the use of a Feistel-like scheme requiring only  $\frac{n}{2} = 64$  bits of tweakey injected in the round function at each iteration.

Thus, we consider the p 64-bit long lanes as p elements of  $GF(2^{64})$  and we multiply each lane by p different  $\alpha_i$  given in Section 2.3.3 in a byte oriented matrix representation. Thus, with our construction,

we obtain the following Vandermonde matrix constructed on  $GF(2^{64})$ :

$$V' = \begin{pmatrix} \alpha_0^0 & \alpha_0^1 & \alpha_0^2 & \cdots & \alpha_0^{r-1} \\ \alpha_1^0 & \alpha_1^1 & \alpha_1^2 & \cdots & \alpha_1^{r-1} \\ \alpha_2^0 & \alpha_2^1 & \alpha_2^2 & \cdots & \alpha_2^{r-1} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ \alpha_{p-1}^0 & \alpha_{p-1}^1 & \alpha_{p-1}^2 & \cdots & \alpha_{p-1}^{r-1} \end{pmatrix}$$

Thus, as  $\forall 0 \le i < r$ , we have chosen the  $\alpha_i$  such that  $r < ord(\alpha_i)$ , we preserve the MDS property induced by the underlying Reed-Solomon code and guarantee that the minimum distance is equal to r - (p + 1)leading to at most (p-1) cancellations on r subtweakeys, seen always, as the XOR of the p lanes. This last choice is a logical one as done in many lightweight block ciphers, such as PRESENT [14], TWINE [58], LBlock [62] or SIMON [4] where the tweakey/key material is loaded in an initial register that is sequentially updated and where the subtweakeys/subkeys are extracted from that register.

We also chose to split the tweakey into p lanes of 64-bit instead of having a big state of  $p \times 64$  bits and to update in parallel those p registers because small updating functions mix their content faster and increase performance. The downside is that each updating function could be attacked independently if their contents were not combined back during the subtweakey extraction which is not the case here.

Let us now explain how we have chosen the different  $\alpha_i$  and the word-ring-LFSRs matrix multiplications at binary level that perform those operations.

We used LFSRs inspired by the results of [7] and [1] on LFSRs. LFSRs are typically used either in Fibonacci or Galois mode. In the first case, many feedbacks are used to influence a single cell while in the second case a single feedback influences many cells. In [7], the authors generalize LFSR beyond Fibonacci/Galois representation by allowing any cell to be used as feedback in any other cell. They call these new LFSRs "ring-LFSRs" because of the rotation occurring at each update. As the LFSRs in [1], the LFSRs chosen here have also a word-oriented structure: instead of performing bit-wise shift at each iteration and having binary feedbacks, they are shifted by one word at each update. As for the feedbacks, they are also word-oriented: one whole word is xored to another after possibly being transformed by a software-friendly operation such as shift or rotation. Those LFSRs are called word-LFSRs by their authors [1]. When a LFSR is both a word and ring LFSR, we call it a word-ring-LFSR. At the same time, they act at word level and they have feedbacks going from some word to some other. Word-ring-LFSRs have thus a smaller diffusion delay than classical Fibonacci or Galois LFSRs.

We have chosen our word-ring-LFSR defined by the matrix M for the  $\alpha_1$ -multiplication with the minimal possible number of shift operations (3 at 8 bits words level) to minimize the number of XOR gates, with a primitive polynomial of degree 64. We chose words of size 8 bits to fit well on software platforms. Then,  $\alpha_2$  and  $\alpha_3$  multiplications are deduced directly using  $M^2$  and  $M^3$ .

Moreover, to construct the matrix  $M_R$  for the  $\alpha_4$  multiplication, we searched for a matrix with 3 shift operations implementing the reciprocal (primitive) polynomial that defines M to ensure that the matrix V' stays a Vandermonde matrix and that the sequences produced when multiplying by  $\alpha_1$  ( $\alpha_2$ and  $\alpha_3$  respectively) and  $\alpha_4$  ( $\alpha_5$  and  $\alpha_6$  respectively) have only a single common value.

We have also chosen the different  $\alpha_i$  with a primitive retroaction polynomial to ensure that the induced periods are maximal: the period for  $\alpha_1, \alpha_2, \alpha_4$  and  $\alpha_5$  is maximal and equal to  $2^{64} - 1$  whereas the period for  $\alpha_3$  and  $\alpha_6$  is equal to  $\frac{2^{64}-1}{3}$ .

Moreover, with this design strategy in mind, we are sure that the entire possible space is reached

discarding the risk of an invariant attack as detailed in Section 3.4.

## 3.3 Security Analysis of the Modes of Operation

## 3.3.1 ⊖CB3

The past year has seen several breakthroughs in the analysis of OCB, starting in October 2018 with the description by Inoue and Minematsu of a practical existential forgery attack [29]. Few weeks after, Poettering [45] extended this result and broke the confidentiality of OCB2, result that was extended further by Iwata [30] who devised a plaintext recovery attack<sup>1</sup>. These attacks were clearly announced by their authors as not applicable to OCB1 and OCB3, so  $\Theta$ CB3 is also safe. To the best of our knowledge, no attacks were devised on  $\Theta$ CB3.

### 3.3.2 SCT-2

To the best of our knowledge, no flaws were found so far in SCT-2 and the results published on Deoxys [63, 41, 18] only target the underlying cipher (that is, Deoxys-BC). In [18], the authors briefly discuss if their attacks on Deoxys-BC could apply once the cipher is used in the corresponding mode, and "argue that [their] attacks are difficult to extend to Deoxys-II". This seems to indicate that the SCT-2 mode does not induce additional flaws to a cipher but on the contrary results in an extra protection coming from the fact that the attacker cannot access the decryption primitive.

To further support that the mode SCT-2 is trusted by the community, we recall here that Deoxys-II was selected after a 5-year process as the first choice for use case 3 ("Defense in depth") in the final Caesar portfolio [16].

## 3.3.3 Security Claims for the Modes

Our security claims for the different variants of LILLIPUT-AE are provided in Table 3.1.

|                                   | Securit    | ty (bits)   |

|-----------------------------------|------------|-------------|

| Goal (nonce-respecting case)      | Lilliput-I | Lilliput-II |

| Key recovery                      | k          | k           |

| Confidentiality for the plaintext | n          | n-1         |

| Integrity for the plaintext       | n          | n-1         |

| Integrity for the associated data | n          | n-1         |

|                                   | Securit    | y (bits)    |

|-----------------------------------|------------|-------------|

| Goal (nonce-misuse case)          | Lilliput-I | Lilliput-II |

| Key recovery                      | k          | k           |

| Confidentiality for the plaintext | none       | n/2         |

| Integrity for the plaintext       | none       | n/2         |

| Integrity for the associated data | none       | n/2         |

Table 3.1: Security goals of LILLIPUT-AE in the nonce-respecting case and in the nonce-misuse case.

The bounds are given in the case of a tag size  $\tau \geq n$ . Should a smaller tag size be used, the security claims will drop according to  $\tau$ . We derived the security bounds from the security proofs of  $\Theta$ CB3 [39] and SCT [44] and we refer to them for more details.

## 3.4 Security Analysis of Lilliput-TBC

We analyze the security of LILLIPUT-TBC regarding classical attacks in the unknown key model and also in the related key model always considering the related tweak model. We will place ourselves for all

<sup>&</sup>lt;sup>1</sup>These three results have been recently merged together in [28]

the attacks in the so-called "paranoid" case, where the worst case is always envisaged even if it could not be reached.

Thus, we divide this section in the following way: we first consider differential/linear cryptanalysis, thus, extending those first results to the case of related key boomerang attacks and then, we give overall bounds for the so-called structural attacks that include impossible differential attacks, zero-correlation attacks, integral attacks and meet-in-the-middle attacks. Then, we take a particular attention on the following special attacks: division property, subspace cryptanalysis, algebraic attack.

Thus, we will first introduce the following bounds that will be used in the rest of this section:

- As the full diffusion is reached after d = 4 rounds for LILLIPUT-TBC, it means that no structural distinguisher can be constructed for more than 2d + 2 rounds (see [8] for a detailed analysis and the security proofs).

- We will also always consider that the number of rounds that can be added to the best distinguisher for the key recovery part at the beginning is equal to d and at the end is also equal to d. Indeed, if a property is found on a single byte at the beginning or at the end of the distinguisher then after d rounds, all the input/output bytes will be influenced, so a key recovery could not exceed those bounds.

- As the tweakey schedule is fully linear and based on the XOR of elements of a Vandermonde matrix, it means that by reversing the linear system, one is able to find in the related tweak/related key models (p-1) cancellations (when p lanes are considered) placed at the best for the attacker.

First, let us precise that to prevent slide attacks [12] and as usually done in other tweakable block cipher proposals, different round constants are added to each subtweakey during the tweakey schedule process. So, we consider LILLIPUT-TBC immune to slide attacks.

## 3.4.1 Differential / Linear Cryptanalysis

To prove the resistance of LILLIPUT-TBC against differential and linear cryptanalysis, we give in Table 3.2 the lower bounds on the minimal number of active S-boxes in the single tweakey model considering no difference in the tweak. Those bounds partly fit with the ones given in [51] for the block cipher LILLIPUT. We have obtained those results using Constraint Programming up to 20 rounds in the single tweakey model. Due to the complexity of the tweakey schedule, we could not derive bounds for the related tweakey models (note that the related tweakey models are not considered for linear cryptanalysis). However, we could place ourselves in the worst case saying that authorizing a particular difference in a single lane i means that the results given in Table 3.2 on r rounds apply for r+2 rounds, in two lanes i and j means that the results given in Table 3.2 on r rounds apply for r+3 rounds, and so on up to p lanes are activated.

Moreover, we use here the fact that, as mentioned in Section 3.2.3, we have  $\delta = 2^{-5}$  and  $\mathcal{L} = 64$  for the chosen S-box.

Thus, with this reasoning, we could derive the following bounds for the different key lengths on the best differential/linear attacks:

- LILLIPUT-TBC-I-128 (t = 192, k = 128):

- Best differential distinguisher on 13 rounds when no difference are introduced at all in the tweakey. Best possible differential attack on 13 + d + d = 13 + 8 = 21 rounds in the same context. If a difference is introduced in b lanes, then the best attack is on 21 + b + 1 rounds, leading to the best possible differential attack when the p lanes have differences equal to 21 + 5 + 1 = 27 rounds.

- With the same reasoning, the best linear distinguisher is on 16 rounds. Then, the best possible linear attack is on 16 + d + d = 16 + 8 = 24 rounds.

- LILLIPUT-TBC-I-192 (t = 192, k = 192):

- Best differential distinguisher on 17 rounds when no difference are introduced at all in the tweakey. Best possible differential attack on 13 + d + d = 17 + 8 = 25 rounds in the same

context. If a difference is introduced in b lanes, then the best attack is on 25 + b + 1 rounds, leading to the best possible differential attack when the p lanes have differences equal to 25 + 6 + 1 = 32 rounds.

- With the same reasoning, the best linear distinguisher is on 23 rounds (extrapolating the results of Table 3.2 up to 48 active S-boxes). Then, the best possible linear attack is on 23 + d + d = 23 + 8 = 31 rounds.

- LILLIPUT-TBC-I-256 (t = 192, k = 256):

- Best differential distinguisher on 24 rounds when no difference are introduced at all in the tweakey (always extrapolating the results of Table 3.2 up to 51 active S-boxes). Best possible differential attack on 24 + d + d = 24 + 8 = 32 rounds in the same context. If, a difference is introduced in b lanes, then the best attack is on 32 + b + 1 rounds, leading to the best possible differential attack when the p lanes have differences equal to 32 + 7 + 1 = 40 rounds.

- With the same reasoning, the best linear distinguisher is on 30 rounds (extrapolating the results of Table 3.2 up to 64 active S-boxes). Then, the best possible linear attack is on 30 + d + d = 30 + 8 = 38 rounds.

- LILLIPUT-TBC-II-128 ( $t=128,\,k=128$ ): The bound for the differential distinguisher is the same than the one given for LILLIPUT-TBC-I-192: the best differential attack works on 21 rounds for the single tweakey model and on 26 rounds when the p lanes have differences. The bound for the linear cryptanalysis is the same than the one given for LILLIPUT-TBC-I-192: 24 rounds.

- LILLIPUT-TBC-II-192 ( $t=128,\,k=192$ ): The bound for the differential distinguisher is the same than the one given for LILLIPUT-TBC-I-192: the best differential attack works on 25 rounds for the single tweakey model and on 31 rounds when the p lanes have differences. The bound for the linear cryptanalysis is the same than the one given for LILLIPUT-TBC-I-192: 31 rounds.

- LILLIPUT-TBC-II-256 ( $t=128,\,k=256$ ): The bound for the differential distinguisher is the same than the one given for LILLIPUT-TBC-I-256: the best differential attack works on 32 rounds for the single tweakey model and on 39 rounds when the p lanes have differences. The bound for the linear cryptanalysis is the same than the one given for LILLIPUT-TBC-I-256: 38 rounds.

Table 3.2: Minimal number of active S-boxes for every round.  $AS_D$  corresponds to the minimal number of S-boxes reached for a differential attack.  $AS_L$  corresponds to the minimal number of S-boxes reached for a linear attack.

| Round  | 1 | 2 | 3 | 4 | 5 | 6 | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

|--------|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| $AS_D$ | 0 | 1 | 2 | 3 | 5 | 9 | 12 | 15 | 17 | 19 | 22 | 24 | 25 | 28 | 29 | 31 | 34 | 40 | 41 | 43 |

| $AS_L$ | 0 | 1 | 2 | 3 | 5 | 8 | 12 | 13 | 15 | 17 | 19 | 22 | 25 | 27 | 30 | 32 | 34 | 38 | 40 | 42 |

## 3.4.2 Related Tweakey Boomerang Attacks

As the attacker could introduce differences both in the tweak and in the key and as our tweakey schedule is linear and could be completely computed according the introduced differences, we could imagine that in a related tweakey boomerang attack, the attacker could find a forward differential trail with (p-1) rounds containing no difference and could also find a backward differential trail with (p-1) rounds without difference. Thus, always considering that the key recovery part at the top of the related tweakey boomerang distinguisher has d=4 rounds and also d=4 rounds at the bottom, we could construct a related tweakey boomerang attack containing  $2 \cdot (p-1) + 8$  rounds at the beginning and at the end, and b rounds in its middle part.

Let us determine how many rounds is b for the different key lengths and considering that between the first differential trail on  $E_0$  and the second differential trail on  $E_1$  with  $e = E_1 \circ E_0$ , we have 2 rounds for free, one because the best coefficient of the BCT is equal to 1 and one because LILLIPUT-TBC is a Feistel-like scheme. Thus, as in a related tweakey boomerang attack, we associated the probability p

of the differential trail for  $E_0$  and q for the differential trail for  $E_1$ . Thus, we expect that the overall probability for b-2 rounds is  $p^2q^2$ .

Thus, for a 256-bit key, we want  $p^2q^2 \leq 2^{-256}$  considering that using several keys and several tweaks we could go beyond the full codebook limit. This leads to  $p \leq 2^{-64}$  considering that p=q. Thus, referring to Table 3.2 with  $\delta_S=2^{-5}$ , the differential trail for  $E_0$  has at most 64/5=12.8 active S-boxes leading to a differential propagating on at most 7 rounds. We apply the same reasoning for  $E_1$ . Thus, the maximal number of rounds a related tweakey boomerang attack could reach is equal to  $7+7+8+2\cdot(p-1)+2=36$  for LILLIPUT-TBC-I-256 and to  $7+7+8+2\cdot(p-1)+2=34$  for LILLIPUT-TBC-II-256. Thus, for a 192-bit key, we want  $p^2q^2 \leq 2^{-192}$ . This leads to  $p \leq 2^{-48}$  considering that p=q and

Thus, for a 192-bit key, we want  $p^2q^2 \le 2^{-192}$ . This leads to  $p \le 2^{-48}$  considering that p = q and to 48/5 = 9.6 active S-boxes for both  $E_0$  and  $E_1$  leading to a differential propagating on at most 6 rounds. Thus, the maximal number of rounds a related tweakey boomerang attack could reach is equal to  $6 + 6 + 8 + 2 \cdot (p - 1) + 2 = 32$  for LILLIPUT-TBC-I-192 and to  $6 + 6 + 8 + 2 \cdot (p - 1) + 2 = 30$  for LILLIPUT-TBC-II-192.

Thus, for a 128-bit key, we want  $p^2q^2 \le 2^{-128}$ . This leads to  $p \le 2^{-32}$  considering that p=q and to 32/5=6.4 active S-boxes for both  $E_0$  and  $E_1$  leading to a differential propagating on at most 5 rounds. Thus, the maximal number of rounds a related tweakey boomerang attack could reach is equal to  $5+5+8+2\cdot(p-1)+2=28$  for LILLIPUT-TBC-I-128 and to  $5+5+8+2\cdot(p-1)+2=26$  for LILLIPUT-TBC-II-128.

## 3.4.3 Structural Attacks