# Non-proprietary FIPS 140-2 Security Policy

Encryption Card ADVA 9TCE-PCN-10GU+AES10G-F

ADVA Optical Networking SE

This Security Policy document may be freely reproduced and distributed as long as its content is not modified, amended or shortened in any way.

### CONTENTS

| 1                            | Introduction                                                      | <br> | <br>5      |

|------------------------------|-------------------------------------------------------------------|------|------------|

| 1.1                          | Purpose                                                           | <br> | <br>6      |

| 1.2                          | References                                                        | <br> | <br>7      |

| 2                            | Module                                                            | <br> | <br>7      |

| <b>2.1</b><br>2.<br>2.<br>2. | 9TCE Encryption Card                                              | <br> | <br>7<br>8 |

| 2.2                          | Module Specification                                              | <br> | <br>12     |

| 2.3                          | Security Level                                                    | <br> | <br>13     |

| <b>2.4</b><br>2.             | Modes of Operation4.1How to Operate the Module in FIPS Approved N |      |            |

| 3                            | Module Ports and Interfaces                                       | <br> | <br>15     |

| 4                            | Roles, Service and Authentication                                 | <br> | <br>15     |

| 4.1                          | Identification and Authentication Policy                          | <br> | <br>15     |

| 4.2                          | Authentication Strength                                           | <br> | <br>       |

| 4.3                          | Authenticated Services                                            | <br> | <br>       |

| 4.4                          | Unauthenticated Services                                          | <br> | <br>       |

| 5                            | Operational Environment                                           | <br> |            |

| 6                            | Cryptographic Key Management                                      | <br> |            |

| 7                            | EMI/EMC                                                           |      | 20         |

| 8                            | Self-Tests                                                        |      |            |

| 8.1                          | Power-On or on Demand Self-Tests                                  |      | <br>       |

| 8.2                          | Conditional Self-Tests                                            |      |            |

| 8.3                          | Self-Test Failure Handling                                        | <br> | 23         |

| 0.5-                         |                                                                   |      |            |

| 9 Acc                                 | ess Control Policy                                                                      | 23                   |

|---------------------------------------|-----------------------------------------------------------------------------------------|----------------------|

| 10 Phy                                | sical Security Policy                                                                   | 23                   |

| 10.1 P                                | hysical Security Mechanisms                                                             | 23                   |

| 11 Sec                                | urity Rules                                                                             | 24                   |

| 12 Miti                               | gation of other Attacks Policy                                                          | 24                   |

| 13 Sec                                | ure Operation                                                                           | 25                   |

| 13.1 In                               | stallation, Initialization and Startup                                                  | 25                   |

| 13.2 G                                | eneral Tamper Seal Placement and Instructions                                           | 26                   |

| 13.3 Ty                               | /pes of Security Seals                                                                  | 27                   |

| 13.3.1                                | Shelf 9 HU Placement Seals                                                              |                      |

| 13.3.2                                | Security Seal Label CFP                                                                 |                      |

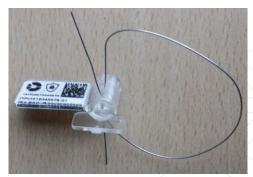

| 13.3.3                                | Security Twist Wire Seal                                                                |                      |

| 13.4 Se                               | ecurity Seal Application Instruction                                                    |                      |

| 13.4.1                                | Security Seal Labels                                                                    |                      |

| 13.4.2                                | Security Twist-Wire Seals                                                               |                      |

| 13.4.3                                | Shelf 1 HU Placement Seals SH1HU-HP/2DC and SH1HU-HP/E-TEMP/2DC                         |                      |

|                                       |                                                                                         |                      |

| 13.4.4                                | Sealing of SH1HU-R/PF                                                                   |                      |

| 13.4.5                                | Sealing of SH7HU(-R)                                                                    |                      |

| 13.4.5<br>13.4.6                      | Sealing of SH7HU(-R)<br>Shelf 9 HU Placement Seals                                      |                      |

| 13.4.5                                | Sealing of SH7HU(-R)                                                                    |                      |

| 13.4.5<br>13.4.6<br>13.4.7            | Sealing of SH7HU(-R)<br>Shelf 9 HU Placement Seals<br>Sealing of 9TCE-PCN-10GU+AES10G-F | 32<br>33<br>34       |

| 13.4.5<br>13.4.6<br>13.4.7            | Sealing of SH7HU(-R)<br>Shelf 9 HU Placement Seals                                      | 32<br>33<br>34       |

| 13.4.5<br>13.4.6<br>13.4.7<br>13.5 Pe | Sealing of SH7HU(-R)<br>Shelf 9 HU Placement Seals<br>Sealing of 9TCE-PCN-10GU+AES10G-F | 32<br>33<br>34<br>35 |

### FIGURES

| Figure 1: 9TCE- based FSP 3000 Systems                                                |      | 6 |

|---------------------------------------------------------------------------------------|------|---|

| Figure 2: Typical application of an ADVA FSP 3000 system                              |      |   |

| Figure 3: 9TCE encryption cards in FSP 3000 encryption solution                       |      |   |

| Figure 4: ADVA 9TCE-PCN-10GU+AES10G-F with backplane interface                        |      |   |

| Figure 5: 9TCE mounted in shelf SH9HU with red dotted line for Cryptographic Boundary | ·    | 9 |

| Figure 6: 9TCE mounted in shelf SH7HU (red dotted line indicating Cryptographic Bound | ary) |   |

| Figure 7: 9TCE mounted in shelf SH1HU (red dotted line indicating Cryptographic Bound | ary) |   |

| Figure 8: 9TCE top view with marked interfaces                                        |      |   |

| Figure 9: 9TCE -front and back view                                                   |      |   |

| Figure 10: 9TCE left view                                                             |      |   |

| Figure 11: 9TCE right view                                                            |      |   |

| Figure 12: 9TCE bottom view                                                           |      |   |

|                                                                                       |      |   |

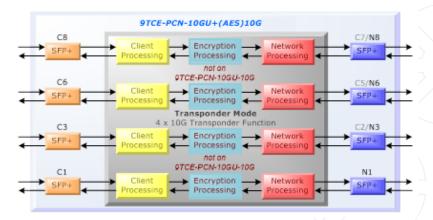

| Figure 13: 9TCE card in multiple transponder mode                   |    |

|---------------------------------------------------------------------|----|

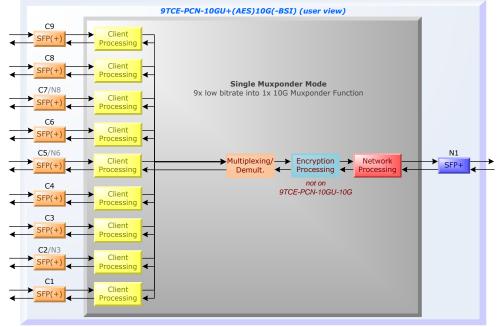

| Figure 14: 9TCE card in single muxponder mode                       | 12 |

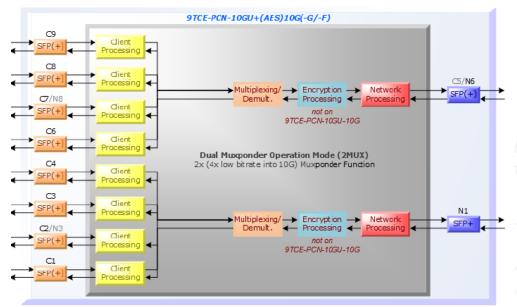

| Figure 15: 9TCE card in dual muxponder mode                         | 12 |

| Figure 16: Sealed ESD bag                                           | 25 |

| Figure 17: Generic security seal label                              | 27 |

| Figure 18: Security seal label CFP                                  |    |

| Figure 19: Security plastic wire coil-in seal package               |    |

| Figure 20: Security plastic wire coil-in seal                       |    |

| Figure 21: Placement of seals on shelf 1 HU, top views              |    |

| Figure 22: Placement seals, shelf 1 HU, placement 1                 |    |

| Figure 23: Placement seals, shelf 1 HU, placement 2                 |    |

| Figure 24: Placement seals, shelf 1 HU, placement 3                 |    |

| Figure 25: Placement seals, shelf 1 HU, placement 4                 |    |

| Figure 26: Placement of seals SH1HU-R/PF front-top view             |    |

| Figure 27: Placement of seals SH1HU-R/PF front-bottom               |    |

| Figure 28: Placement of seals SH1HU-R/PF left side positions        |    |

| Figure 29: Placement of seals SH1HU-R/PF right side positions       |    |

| Figure 30: Placement of seal SH1HU-R/PF right side position         |    |

| Figure 31: Placement of seal SH7HU rear side                        |    |

| Figure 32: Placement of seal SH7HU (-R) rear side                   |    |

| Figure 33: Seals rear side shelf 9HU                                |    |

| Figure 34: Seals cover rear edge shelf 9 HU                         |    |

| Figure 35: Placement of twist seal in SH1HU configuration           |    |

| Figure 36: Placement of twist seal in SH7HU and SH9HU configuration |    |

|                                                                     |    |

### TABLES

| Table 1: Cryptographic module configurations                                           |              | <br>             | 5    |

|----------------------------------------------------------------------------------------|--------------|------------------|------|

| Table 2: Module validation security levels                                             |              |                  | 13   |

| Table 3: Cryptographic algorithms                                                      |              |                  | 14   |

| Table 4: Cryptographic algorithms of the embedded module #2628 used by the cryptograph |              |                  |      |

| Table 5: Roles and required encryption identification and authentication               |              | <br><u>\</u> ,/. | 15   |

| Table 6: Strenath of authentication mechanisms                                         |              | <br>             | 16   |

| Table 7: Roles and services authenticated                                              |              | <br>             | 17   |

| Table 8: Roles and services unauthenticated                                            |              | <br>             | 18   |

| Table 9: Cryptographic key, CSP and PSP management                                     | .,           | <br>             | 20   |

| Table 10: Power-up self-tests                                                          |              |                  | . 22 |

| Table 11: Conditional tests                                                            |              |                  |      |

| Table 12: Inspection/testing of physical security mechanisms                           | \ <i>,</i> / | <br>             | 24   |

| Table 13: Mitigation of other attacks                                                  | ,            | <br>,            | 25   |

| Table 14: Definition and acronyms                                                      |              |                  | 36   |

### 1 Introduction

This is the non-proprietary FIPS 140-2 Security Policy for the encryption card ADVA 9TCE-PCN-10GU+AES10G-F (also referred to as "9TCE" or as "9TCE encryption card" hereinafter). The cryptographic boundary of the module in the sense of FIPS 140-2 is the configured 9TCE encryption card within customer-chosen combinations of shelves with modular functionality and density. For clarity, the cryptographic module in the meaning of FIPS 140-2 consists of the 9TCE encryption card below.

The module is a multiple-chip embedded cryptographic module that is covered with a commercial-grade metal cover that includes components equipped for physical security and assurance of opacity. They belong to the module in the sense of FIPS 140 and are located within the cryptographic boundary, but contribute exclusively to the physical security of the module.

The module is a part of the ADVA Fiber Service Platform (FSP) 3000 scalable optical data transport system. The module is a transponder for core telecommunication networks, and transports plaintext 10GbE or OUT-2 client-side data services to and from the encrypted network interface. The module performs key agreement and synchronization with a far-end network peer to support AES encryption of the network link.

The FIPS validation covers the following combinations of hardware and firmware of the 9TCE encryption card and either one of the listed shelves (firmware 191.4.8 contains some stability fixes, while the services and cryptographic functionality of the module stays the same as in 172.25.7; firmware versions for microcontroller part and FPGA part always correspond to each other one-to-one in a module, no mixing of versions is possible):

| Component                                                   | Version               | OE Processor                  | Part Number Hardware                        |

|-------------------------------------------------------------|-----------------------|-------------------------------|---------------------------------------------|

| Hardware:<br>Encryption Card ADVA<br>9TCE-PCN-10GU+AES10G-F | HW B-1.01             |                               | 1063707672-01 F7/9TCE-PCN-10GU+AES10G-<br>F |

| Firmware:                                                   |                       |                               |                                             |

| microcontroller part                                        | 172.25.7 /<br>191.4.8 | Coldfire MCF5282              | n/a                                         |

| FPGA part                                                   | 172.25.7 /<br>191.4.8 | Xilinx Kintex UltraScale FPGA | n/a                                         |

| Configured in one of the following shelves:                 |                       |                               |                                             |

| 9HU shelf (SH9HU)                                           | HW 2.01               | n/a                           | 1078700121 F7/SH9HU                         |

| 7HU shelf (SH7HU)                                           | HW 2.05               | n/a                           | 0078700101 F7/SH7HU                         |

| 7HU shelf (SH7HU-R)                                         | HW 2.05               | n/a                           | 0078700111 F7/SH7HU-R                       |

| 1HU shelf (SH1HU-R/PF)                                      | HW 1.01               | n/a                           | 1078700060-01 F7/SH1HU-R/PF                 |

| 1HU shelf (SH1HU-HP/2DC)                                    | HW 2.11               | n/a                           | 1078700144 F7/SH1HU-HP/2DC                  |

| 1HU shelf (SH1HU-HP/E-<br>TEMP/2DC)                         | HW 1.01               | n/a                           | 1078700145-01 F7/SH1HU-HP/E-TEMP/2DC        |

| Tamper evident seals<br>(delivery):                         | n/a                   | n/a                           | 1013700030-01                               |

| SEAL/FIPS-GENERAL                                           |                       |                               |                                             |

| SEAL/FIPS-WIRE                                              | n/a                   | n/a                           | 1013700032-01                               |

| Tamper evident seals<br>(ordered separately):               | n/a                   | n/a                           | BC00000738                                  |

| SEAL/FIPS-GENERAL/5                                         |                       |                               |                                             |

Table 1: Cryptographic module configurations

Each of the module configurations has to be equipped to assure the opacity as required by FIPS 140-2 and the security as specified in Module and System Specification and User Documentation for approved operation. (Details in section 13, Secure Operation).

The module configuration within the shelf defines the Cryptographic Boundary. The shelf is part of the module, but contributes exclusively to the physical security, to ensure that the module is opaque within the visible spectrum. By tamper evident seals applied to 9TCE encryption card and shelf, tamper evidence is ensured for the module.

Figure 1: 9TCE- based FSP 3000 Systems

### 1.1 Purpose

This document was prepared as part of the FIPS 140-2 validation process.

This document describes, how the module meets the security requirements of FIPS 140-2. In addition, individuals and organizations receive instructions on how to use the product in a secure mode as approved by FIPS. The target group of this document is anyone who wants to use one of these products or wants to integrate it into a solution that meets the requirements of FIPS 140-2.

With the exception of this Non-Proprietary Security Policy, the FIPS 140-2 validation submission documentation is ADVAproprietary and is releasable only under appropriate non-disclosure agreements. For access to these product documents, please contact ADVA:

ADVA Optical Networking SE Fraunhoferstr. 9a 82152 Martinsried/München Germany Phone +49(0)89-890665-0 Fax +49(0)89-890665-699 https://www.adva.com

### 1.2 References

This document describes, how the module meets the security requirements of Federal Information Processing Standards (FIPS) Publication 140-2.

More details regarding FIPS 140-2 standards, qualification and the Cryptographic Module Validation Program (CMVP) are available on the NIST website, see <u>https://csrc.nist.gov/projects/cryptographic-module-validation-program.</u>

#### 2 Module

- 2.1 Overview

- 2.1.1 Typical application of FSP3000 system:

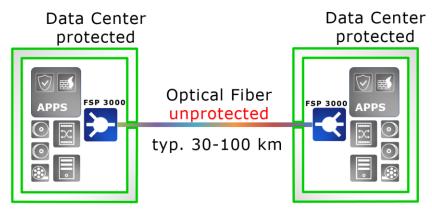

Figure 2: Typical application of an ADVA FSP 3000 system

In a typical application, the FSP 3000 containing the module is located in racks in a data center. The fiber connection between the data centers is completely owned by the user or a "service", which is sold by a service provider. The physical access to the equipment is controlled. Access is only granted to persons, which need to have access for restricted time. The access time is logged.

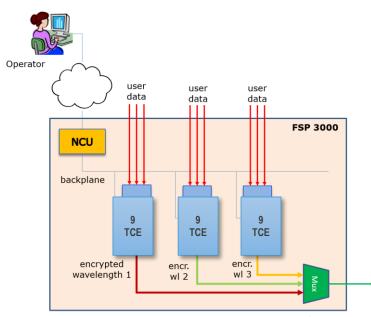

Figure 3: 9TCE encryption cards in FSP 3000 encryption solution

A typical encryption solution for the optical fiber connection with FSP 3000 consists of the following components: One or more FSP 3000 shelves including shelf controller, fan unit, power supply, and one network control unit (NCU) in the main shelf, multiple encryption cards and optical filters.

The 9TCE module interfaces supports up to ten SFP and SFP+ pluggable optics providing the optical-to-electrical conversion (and vice versa), collection of physical layer performance monitoring and alarm monitoring for each client service. The client interfaces support services with data rates ranging between 10Mbit/s (Ethernet) and 10.709Gbit/s (OTU2) while the network interfaces support data rates of 10.709Gbit/s (OTU2), 11.095Gbit/s (OTU2e) and 10.975Gbit/s (OTU2fc). This user data stream is encrypted, framed in OTU frames, protected with error correction codes and transmitted to the far-end side. The receiving side decrypts the data and sends it to the corresponding clients.

### 2.1.2 9TCE Encryption Card

The 9TCE-PCN-10GU+AES10G-F encryption card (abbreviated in this document as 9TCE) is a plug-in card for the FSP 3000 system. The 9TCE alone is implementing all logics/functionality as required by FIPS 140-2, yet the 9TCE alone is not the cryptographic module in the meaning of FIPS140-2. To satisfy the physical security requirements of FIPS 140-2 (mainly the opacity requirements), the 9TCE has to be mounted in one of the shelves as stated in the following section "Cryptographic Boundary" (see there for images of 9TCE and the corresponding shelves).

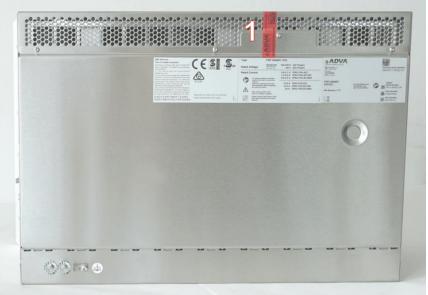

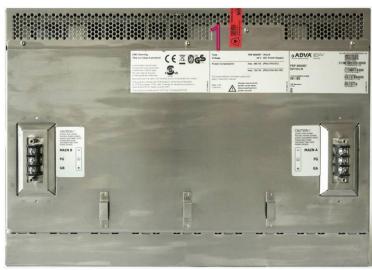

Figure 4: ADVA 9TCE-PCN-10GU+AES10G-F with backplane interface

The 9TCE shows its current status with LEDs on the front panel and NCU notifications. Please see Section 2.1.3 for pictures of the cryptographic module an the available shelves in can be operated in.

The NCU has contact to all modules, using the backplane with 100 Mbit/s Ethernet and VLANs. Please take note that the NCU is not part of the cryptographic module, it is an input/output device for the module only.

Furthermore, 9TCE contains an embedded cryptographic module, "StarSign Crypto-USB Token S powered by Sm@rtCafé Expert 7.0 Secure Element" by Giesecke+Devrient Mobile Security GmbH. This embedded module is a single-chip cryptographic module in a VQFN32 IC package, which is firmly integrated into the 9TCE using surface-mounting

technology (it is used as a seed source for 9TCE DRBG, compare CMVP cert. #2628 and corresponding security policy, and DRBG cert. #455).

#### 2.1.3 Cryptographic Boundary

The Cryptographic Boundary is defined as the entire metal case of the 9TCE card include the outer range of the configured shelf, including all hardware, software and firmware encapsulated and tamper response detection within (as 9TCE contains the embedded cryptographic module, "StarSign Crypto-USB Token S powered by Sm@rtCafé Expert 7.0 Secure Element" by Giesecke+Devrient Mobile Security GmbH, this embedded module is also located inside the cryptographic boundary). The interfaces are all traces that cross the Cryptographic Boundary.

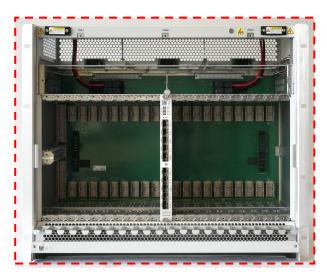

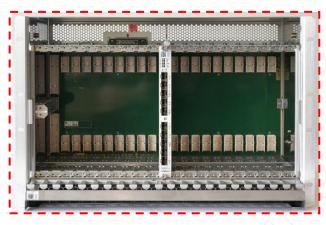

The physical forms of the different shelves the cryptographic module can be operated in are shown in Figure 5 to Figure 7. Here the 9TCE encryption board is integrated to each available shelf listed in Table 1. Figure 8 to Figure 12 show the 9TCE encryption board

Figure 5: 9TCE mounted in shelf SH9HU with red dotted line for Cryptographic Boundary

Figure 6: 9TCE mounted in shelf SH7HU (red dotted line indicating Cryptographic Boundary)

*Figure 7: 9TCE mounted in shelf SH1HU (red dotted line indicating Cryptographic Boundary)*

Figure 8: 9TCE top view with marked interfaces

Figure 9: 9TCE -front and back view

Figure 10: 9TCE left view

Figure 11: 9TCE right view

Figure 12: 9TCE bottom view

The primary purpose of the 9TCE encryption card is to secure data traffic over fiber-optical lines. The 9TCE encryption card supports multiple network interfaces and each interface runs independent encryption engines with independent management interface (configuration, fault, performance management). Encryption configuration and operation are managed individually per network port. There is only one Crypto Officer Password per 9TCE used to control all encryption related actions on any network port. The 9TCE (as a whole, not the network ports individually) can be configured to "Transponder Mode" or "Muxponder Mode", and some of the ports can act either as client or as network depending on configuration. The following figure shows the 9TCE card in multi transponder mode with 4 client ports and 4 network ports.

Figure 13: 9TCE card in multiple transponder mode

The following figure shows the 9TCE card in single muxponder mode with 9 client ports and 1 network port.

Figure 14: 9TCE card in single muxponder mode

The following figure shows the 9TCE card in dual muxponder mode with 8 client ports and 2 network port.

Figure 15: 9TCE card in dual muxponder mode

### 2.2 Module Specification

When placed inside one of the shelves listed in Table 1, the 9TCE card is shielded with metal on front, left and right side. It has openings at its top, bottom and back side, which are required for air flow and cooling. All sensitive components are inside the shielding. The cover is fixed with rivets to make it hard for an attacker to open and modify it. Figures 8 to 12 show the openings in the cover to allow air flow when 9TCE is mounted in a shelf. Electronic components of the 9TCE cannot be seen through these openings, when 9TCE is mounted in a shelf as given in table 1. The 9TCE cover and the layout of the PCB of 9TCE, in combination with the corresponding shelf, guarantee that sensitive components of 9TCE.

(e.g., micro controller, FPGA, seed source, or IC used for password storage) are not reachable and that IC descriptions are not visible.

### 2.3 Security Level

The module meets the overall requirements applicable to Level 2 security of FIPS 140-2. In section "Cryptographic Key Management" and "Design Assurance" level 3 is reached. The module has a 128-bit overall security strength.

| Security Requirements Section      | Level |

|------------------------------------|-------|

| Cryptographic Module Specification | 2     |

| Module Ports and Interfaces        | 2     |

| Roles, Services and Authentication | 2     |

| Finite State Model                 | 2     |

| Physical Security                  | 2     |

| Operational Environment            | N/A   |

| Cryptographic Key Management       | 2     |

| EMI/EMC                            | 2     |

| Self-Tests                         | 2     |

| Design Assurance                   | 3     |

| Mitigation of Other Attacks        | 2     |

Table 2: Module validation security levels

### 2.4 Modes of Operation

The module is designed to exclusively run in the Approved mode of operation. In this mode, the module supports the following FIPS-approved cryptographic algorithms (certificate numbers with prefix "C" belong to the firmware version 172.25.7, certificate numbers with prefix "A" belong to firmware version 191.4.8, no mixing of versions is possible in one module):

| CAVP Cert                                     | Algorithm | Standard(s)             | Mode /<br>Method              | Key Lengths,<br>Curves or Moduli | Use                                                                        |

|-----------------------------------------------|-----------|-------------------------|-------------------------------|----------------------------------|----------------------------------------------------------------------------|

| #C667 for FW 172.25.7                         | AES       | FIPS 197,<br>SP 800-38A | CTR Encryption/<br>Decryption | 256 bits                         | AES-CTR User Data<br>Encryption/<br>Decryption on FPGA                     |

| #A887 for FW 191.4.8                          |           |                         | ECB Encryption/<br>Decryption | 256 bits                         | AES-CTR User Data<br>Encryption/<br>Decryption on FPGA, see<br>note below. |

| #C666 for FW 172.25.7<br>#A886 for FW 191.4.8 | AES       | FIPS 197,<br>SP 800-38A | ECB Encryption/<br>Decryption | 128 bits<br>256 bits             | Secure Storage<br>CTR_DRBG (in 9TCE<br>firmware)                           |

| #C666 for FW 172.25.7<br>#A886 for FW 191.4.8 | HMAC      | FIPS 198-1              | SHA-256                       | 256-bit hash length              | Key Confirmation<br>according to SP 800-56Ar3<br>Sec. 6.1.1.5.3            |

| #C666 for FW 172.25.7<br>#A886 for FW 191.4.8              | SHS                                | FIPS 180-4                                                           | SHA-256,<br>SHA-512                                                                                                   | 256-bit hash length<br>512-bit hash length | Secure Hash                                                                                                                                        |

|------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| #C666 for FW 172.25.7<br>#A886 for FW 191.4.8              | DRBG                               | SP 800-90Ar1                                                         | CTR_DRBG                                                                                                              | 256 bits of strength                       | Deterministic Random Bit<br>Generator (in 9TCE<br>firmware)                                                                                        |

| #C666 for FW 172.25.7<br>#A886 for FW 191.4.8              | RSA                                | FIPS 186-4                                                           | SHA-256<br>RSASSA-PKCS1-<br>v1_5,<br>RSASSA-PSS                                                                       | 4096 bits                                  | Digital Signature<br>verification                                                                                                                  |

| Vendor affirmed for<br>FW 172.25.7<br>#A886 for FW 191.4.8 | KAS                                | SP 800-56Ar3<br>(vendor affirmed<br>per IG D.1-Rev3)<br>SP 800-56Ar3 | FFC (dhHybrid1,<br>C(2e, 2s, FFC DH)<br>Scheme) with One-<br>Step Key Derivation<br>using SHA-512 per<br>SP 800-56Cr2 | 3072 bits                                  | Key Establishment<br>(key establishment<br>methodology provides 128<br>bits of encryption strength)                                                |

| #A886 for FW 191.4.8                                       | Safe<br>Primes Key<br>Generation   | SP 800-56Ar3                                                         | _                                                                                                                     | MODP-3072                                  | Generation of DH key pairs<br>(static and ephemeral key<br>pairs) according to SP 800-<br>56Ar3 Sec. 5.6.1.1.1 and<br>5.6.1.1.4 for use in the KAS |

| #A886 for FW 191.4.8                                       | Safe<br>Primes Key<br>Verification | SP 800-56Ar3                                                         | -                                                                                                                     | MODP-3072                                  | Used in the KAS for key validation according to SP 800-56Ar3 Sec. 5.6.2.3.1                                                                        |

| Vendor affirmed                                            | CKG                                | IG D.12                                                              | FFC (DH)                                                                                                              | 3072 bits                                  | Generation of DH key pairs<br>(static and ephemeral key<br>pairs) according to SP 800-<br>133r2 Sec. 5.2.<br>W.r.t. SP 800-133r2 Sec. 4.           |

|                                                            |                                    |                                                                      |                                                                                                                       |                                            | no XOR is used.                                                                                                                                    |

| Vendor affirmed                                            | CKG                                | IG D.12                                                              | AES                                                                                                                   | 128 bits                                   | Generation of the storage<br>extension key during<br>module initialization.                                                                        |

|                                                            |                                    |                                                                      | 2: Chintographic ala                                                                                                  |                                            | W.r.t. SP 800-133r2 Sec. 4,<br>no XOR is used.                                                                                                     |

Table 3: Cryptographic algorithms

The following algorithms listed in the CAVP certificates referenced above are not used by the cryptographic module:

- AES-ECB of #C667 and #A887,

- DSA KeyGen (FIPS186-4) of #A886 (key generation for the KAS is done with safe primes).

Note regarding AES-CTR: In case of #A887, CAVP testing for AES-CTR was not available due to the way the counter is constructed and AES-ECB was tested instead. The module uses AES-CTR for user data encryption/decryption.

Note regarding KAS-SSC: Testing of SP800-56A in #C666 is used for vendor affirmation of SP800-56Ar3 following IG D.1-Rev3.

By verifying that the firmware version, identified using the 'Get Version' service, matches each of the validated firmware components versions listed in section 1, the operator can be assured that the module is running in the Approved mode. A SHA-256 hash value is included in the version information for unambiguous identification of the firmware of the module. Furthermore, no bypass mode and no maintenance mode are implemented in the module.

The following table identifies cryptographic algorithms implemented in the embedded module #2628 used by the cryptographic module.

| CAVP Cert | Algorithm | Standard(s) | Mode /<br>Method | Key Lengths,<br>Curves or Moduli | Use                                                                     |

|-----------|-----------|-------------|------------------|----------------------------------|-------------------------------------------------------------------------|

| #455      | DRBG      | SP 800-90A  | CTR_DRBG         | 256 bits of strength             | Seeding of the<br>cryptographic module's<br>DRBG (see <i>Table 3</i> ). |

Table 4: Cryptographic algorithms of the embedded module #2628 used by the cryptographic module

The embedded module #2628 implements an NDRNG which is a non-approved function but allowed in the approved mode of operation. It is used to seed the DRBG of the embedded module. Besides that, the cryptographic module performs additional self-tests on the NDRNG output.

#### 2.4.1 How to Operate the Module in FIPS Approved Mode

The module is operated in its Approved mode of operation, if instructions as given in section 13 are regarded, see:

- 13.1 Installation, Initialization and Startup

- 13.2 General Tamper Seal Placement and Instructions

- 13.3 Types of Security Seals

- 13.4 Security Seal Application Instruction

- 13.5 Periodical Inspection

### 3 Module Ports and Interfaces

The Module's physical interfaces (Figure 7) are the traces that cross the perimeter of the physical Cryptographic Boundary. The following logical interfaces are defined according to FIPS 140-2:

- Data input interface: receiving plaintext data from the local user or receive encrypted data from the far-end module via optical interfaces.

- Data output interface: send decrypted data to the local user or send encrypted data to the far-end module via optical interfaces.

- Control input interface: send control information to the module via backplane interface.

- Control input/output interface: A logical optical interface is used for key agreement and synchronization.

- Status output interface: get status information by management interface via backplane or by observing the LEDs in the front panel.

- Power input interface via backplane and output interface for SFP connector.

### 4 Roles, Service and Authentication

Crypto Officer is connected to the module via the backplane (using an NCU as input/output device). The User of the module (i.e. a remote module of the same type) is connected via optical link, using in-band channels for communication. The module also provides a couple of services without authentication and assuming Crypto Officer or User role.

The module supports concurrent operators only in terms of the Crypto Officer and the User (i.e. remote module) using the module at the same time, but both using disjoint sets of services over backplane or optical link, respectively.

### 4.1 Identification and Authentication Policy

The module supports two distinct roles with the following authentication:

| Role                    | Type of Authentication                          | Authentication Data / CSP        | 2 |

|-------------------------|-------------------------------------------------|----------------------------------|---|

| User (U)                | Role-based authentication with<br>Pairing Token | Pairing token(s) (static DH Key) | / |

| Crypto- Officer<br>(CO) | Role-based authentication with password         | Crypto Officer password          |   |

Table 5: Roles and required encryption identification and authentication

A complete description of all the management and configuration capabilities can be found in the User Documentation.

### 4.2 Authentication Strength

| Authentication                               | Authentication Data/Strength                                                                                                                                                                                                                                                                                             |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Role based authentication with password      | Minimum password length is 10 characters. Assuming random usage of 26 lower case letters, 26 upper case letters and 10 decimal digits, this makes a total of $(26 + 26 + 10)^{10}$ password combinations.                                                                                                                |

|                                              | After 3 failed password attempts, the CO account is locked for 10 minutes. In one minute, therefore only three attempts are possible. The probability of successfully authenticating to the module within one minute is $3/(26 + 26 + 10)^{10}$ , which is less than one in 100,000.                                     |

| Role based authentication with Pairing token | Pairing token length is at least 3072 bit, this defines a strength of 128 bit at least. The probability for a successful random authentication attempt is therefore 1/2^128.<br>After three failed attempts, the key agreement is locked and must be enabled by the CO. In one minute, therefore only three attempts are |

| Tabla 6: 6t                                  | possible. The probability of successfully authenticating to the module within<br>one minute is 3/(2^128), which is less than one in 100,000.                                                                                                                                                                             |

Table 6: Strength of authentication mechanisms

### 4.3 Authenticated Services

The services for authorized operators (Crypto Officer (CO); User (U)) are listed below with access and use (r = read; w=write; x= execute) of CSPs. CSPs are erased on tamper detection, on zeroization command, on removal of module (further referred as 'erase of CSPs')

| Service                 | Role | Description                                                                                                                                                                    | Cryptographic Keys<br>and CSPs | Type(s) of Access |

|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------|

| Initial setup of module | CO   | Set initial Crypto Officer<br>password<br>and set default crypto<br>parameters<br>Need: CO password<br>Modify: CO password<br>stored as SHA-256<br>protected in security chip  | CO password                    | (w/x)             |

| Start pairing           | СО   | Delete old pairing token<br>and generate new pairing<br>token<br>Need: CO password<br>Modify: local pairing<br>token<br>stored as DH private key<br>protected in security chip | CO password<br>pairing token   |                   |

| Accept fingerprint      | СО   | Establish pairing token<br>Need: CO password<br>stored as DH public key<br>protected in security chip                                                                          | CO password<br>pairing token   | (w/x)             |

| Change CO password                         | CO | Change Crypto Officer<br>password<br>Need: CO password<br>Change: CO password<br>stored as SHA-256<br>protected in security chip | CO password                                         | (w/x)                             |

|--------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------|

| Allow firmware update                      | СО | Allow firmware update<br>and set expected target<br>revision.                                                                    | CO password<br>allow update<br>target revision      | (w/x)                             |

| Activate firmware<br>update                | СО | Activate new firmware<br>revision located on<br>standby image.                                                                   | CO password                                         | (x)<br>(=new firmware<br>version) |

| Cold start                                 | СО | Cold start with current<br>firmware image<br>Required: Crypto Officer<br>password                                                | CO password                                         | (X)                               |

| Configure session-key<br>lifetime          | СО | Established session-keys<br>may be used for a limited<br>time, even if key-<br>agreement processes has<br>failed.                | CO password<br>Key-lifetime                         | (r/w/x)                           |

| Initiate self-test                         | СО | Initiated Self-Test                                                                                                              | CO password<br>as defined in Self-test<br>section 8 | (x)                               |

| Reset key establishment<br>failure counter | СО | Reset Counter                                                                                                                    | CO password<br>Key establishment<br>failure counter | (w/x)                             |

| Reset to factory-default<br>("Zeroize")    | СО | Set module to well-<br>defined initial state. Clear<br>stored passwords<br>(force zeroization)                                   | CO password,<br>all CSPs,<br>all crypto parameters  | (w/x)                             |

| key-establishment                          | U  | Do key-establishment                                                                                                             | Pairing token<br>Session keys<br>RBG                | (r/w/x)                           |

| Link encrypt/<br>decrypt                   | U  | encrypt/decrypt data                                                                                                             | Session keys                                        | (r/w/x)                           |

Table 7: Roles and services authenticated

N.B. Firmware update is a two-step process. First, the new firmware is loaded into so-called standby image, i.e. the loading is performed, though the new firmware is not activated yet (even after a reset or power-cycle of the module). Only after the second step, in which the new firmware is explicitly activated by the CO, the former standby image becomes the active image (executed during subsequent power-ons of 9TCE). This allows pre-distribution of firmware updates to several copies of 9TCE, while cryptographic service is not affected at that time. The new firmware is then activated everywhere and all copies of 9TCE are restarted, ideally at the same time, to minimize downtime of the cryptographic services. In case of a firmware update performed, the resulting new configuration may no longer be validated (unless the 9TCE has been (re-) validated with new firmware version before).

### 4.4 Unauthenticated Services

The module provides a limited number of services for which the Crypto Officer or User is not required:

| Service                     | Description                                                | Input | Output                                                                                  | ~      |

|-----------------------------|------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------|--------|

| Self Test                   | Self-Test without command<br>invocation<br>(e.g. Power-On) | None  | Status output                                                                           | $\sim$ |

| Status LED<br>(Show Status) | Show Status LED without command invocation                 | None  | Status information about the state of the encryption service and the self-test results. |        |

| Service                            | Description                                                                                                                               | Input                                      | Output                                   |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------|

| Get Status (Show Status)           | Get actual status information<br>(e.g. serial number, HW revision,<br>FW version and checksum,<br>tamper, battery state, error<br>state,) | Command<br>Parameter                       | Response<br>Actual status information    |

| Send notification<br>(Show Status) | Send notification to NCU                                                                                                                  | Event                                      | Event information                        |

| Copy firmware                      | Copy firmware image to inactive<br>FW memory of module<br>("standby image")                                                               | FW Image<br>and Signature                  | Status of successful copy to module      |

| Validate new firmware              | Validate firmware approved signature                                                                                                      | FW and signature<br>Public keys running FW | Accept new FW or delete new<br>FW image. |

Table 8: Roles and services unauthenticated

### 5 Operational Environment

The FIPS 140-2 section 6 'Operational Environment requirements' are not applicable, because the module does not contain a modifiable operational environment.

To load new firmware image into the module, a firmware load test according to FIPS 140-2 is done. This requires the verification of a digital signature.

### 6 Cryptographic Key Management

The module uses a FIPS-Approved SP 800-90Ar1 CTR\_DRBG to generate cryptographic FFC key pairs according to NIST SP 800-56Ar3. The randomness source used, implemented in the cryptographic module "StarSign Crypto-USB Token S powered by Sm@rtCafé Expert 7.0 Secure Element" by Giesecke+Devrient Mobile Security GmbH (referred to as "embedded module" in this SP), is an approved DRBG (compare CMVP cert. #2628 and DRBG cert. #455).

The 9TCE key management mechanisms, random number and key generation, key establishment, key distribution, key entry/output, key storage, and key zeroization is shown in the following section. Secrets and private key material (CSP) as well as public security parameters (PSPs) managed by the module will be zeroized as described in the following table:

| CSP                      | CSP Type        | Generation / Input              | Output                    | Storage<br>Location                                        | Zeroization                                      | Usage                                                                                                                                                                                             |

|--------------------------|-----------------|---------------------------------|---------------------------|------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CO Password              | Password        | CO / NCU                        | Never exits<br>the module | Tamper<br>protected in<br>security chip as<br>SHA-256 hash | Zeroization when<br>tampered and per<br>command. | Authenticate<br>Crypto Officer<br>Services                                                                                                                                                        |

| Storage<br>extension key | 128-bit AES key | Generation at<br>initialization | Never exits the module    | Tamper<br>protected in<br>security chip                    | Zeroization when<br>tampered and per<br>command. | 128-bit key for<br>access to<br>nonvolatile<br>secure storage in<br>internal module<br>and AES-ECB<br>encryption of<br>material stored in<br>that module<br>used for R/W of<br>security chip data |

| Pairing token<br>DH private<br>static key<br>(stored in<br>security chip)      | 3072-bit DH<br>key                                                              | The module's static<br>key is generated<br>internally req. by CO                | Never exits<br>the module                                                                                   | Tamper<br>protected in<br>security chip                         | Zeroization when<br>tampered and per<br>command.                                                                                           | Establishment of<br>AES session key,<br>Authentication                                    |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Pairing token<br>DH private<br>static key<br>(stored in<br>internal<br>module) | 3072-bit DH<br>key                                                              | The module's static<br>key is generated<br>internally req. by CO                | Never exits<br>the module                                                                                   | Internal module<br>(encrypted with<br>Storage<br>extension key) | Tamper protected<br>by automated<br>zeroization of the<br>storage-extension<br>key in the security<br>chip.<br>Zeroization per<br>command. | Establishment of<br>AES session key,<br>Authentication                                    |

| DH<br>ephemeral<br>private key                                                 | 3072-bit DH<br>key                                                              | The module's private<br>key is generated<br>internally                          | Never exits the module                                                                                      | RAM µCM                                                         | After key<br>agreement.                                                                                                                    | Establishment of AES session key                                                          |

| Shared secret                                                                  | Share secret as<br>used in key<br>agreement<br>according to<br>SP 800-56Ar3     | Intermediate result of<br>key-agreement<br>process                              | Never exits<br>the module                                                                                   | RAM µCM                                                         | After key<br>agreement.                                                                                                                    | Establishment of<br>AES session key                                                       |

| HMAC key                                                                       | HMAC 160-bit<br>key used in key<br>confirmation<br>according to<br>SP 800-56Ar3 | Intermediate result of<br>key-agreement<br>process                              | Never exits<br>the module                                                                                   | RAM µCM                                                         | After key<br>agreement.                                                                                                                    | Establishment of<br>AES session key                                                       |

| AES key<br>(and IV)                                                            | 256-bit AES<br>key<br>(96-bit IV)                                               | Result of key<br>agreement process                                              | Never exits<br>the module                                                                                   | RAM µCM<br>until send to<br>FPGA                                | Zeroized in RAM<br>µCM after the key<br>was written to the<br>FPGA.<br>Tamper detection,<br>every new key in<br>FPGA or per<br>command.    | Session-key for<br>encrypting user<br>data                                                |

| CTR_DRBG<br>state                                                              | V and key<br>values acc. to<br>SP800-90Ar1,<br>256 bits each                    | CTR_DRBG state<br>values as seeded and<br>updated during<br>DRBG usage          | Internally used<br>for DH private<br>key generation<br>using the<br>CTR_DRBG.<br>Do not exit the<br>module. | μCm                                                             | Power cycle                                                                                                                                | Generate private<br>DH keys.<br>(for 1 of 4 ports)<br>and<br>Random delay<br>values.      |

| DRBG output/<br>CTR_DRBG<br>seed                                               | Seed, 384 bits                                                                  | CTR_DRBG is seeded<br>using output of<br>DRBG of embedded<br>module             | Seed does not<br>exit the module                                                                            | Hardware<br>(cert #2628)                                        | Firmware (DRBG<br>cert #2628)                                                                                                              | DRBG of<br>embedded<br>module (DRBG<br>cert. #455) used<br>as seed source<br>for CTR_DRBG |

| Firmware                                                                       | SHA-256/<br>RSA-PSS-4096<br>signature                                           | Generated by ADVA<br>during firmware<br>generation.<br>Sent to module by<br>NCU | SHA 256 exits the<br>module for<br>verification                                                             | Flash memory                                                    | Firmware update<br>delete old image                                                                                                        | Firmware update                                                                           |

| PSP                                                                            | PSP Type                                                                        | Generation / Input                                                              | Output                                                                                                      | Storage<br>Location                                             | Zeroization                                                                                                                                | Usage                                                                                     |

| Pairing token<br>DH static<br>public key<br>(stored in<br>security chip)       | 3072-bit DH<br>key                                                              | The module's public<br>key is generated<br>internally                           | Public static key<br>exits the module<br>in key-<br>establishment<br>process                                | Security chip                                                   | Tamper protected<br>in HW chip.<br>Zeroization when<br>tampered and per<br>command.                                                        | Establish session<br>key<br>authentication                                                |

| Pairing token<br>DH static<br>public key<br>(stored in<br>internal<br>module) | 3072-bit DH<br>key                    | The module's public<br>key is generated<br>internally                             | Public static key<br>exits the module<br>in key-<br>establishment<br>process                                    | Internal module<br>(encrypted with<br>Storage<br>extension key) | Tamper protected<br>by automated<br>zeroization of the<br>storage-extension<br>key in the security<br>chip.<br>Zeroization per<br>command.                                                      | Establish session<br>key<br>authentication |

|-------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| DH<br>ephemeral<br>public key                                                 | 3072-bit DH<br>key                    | The module's public<br>key is generated<br>internally                             | Public key exit<br>the module in<br>key-<br>establishment<br>process                                            | RAM µCM<br>send to<br>far end µCM                               | After key<br>agreement<br>overwritten with<br>zero.                                                                                                                                             | Establish session<br>key agreement         |

| DH static<br>public key of<br>external<br>device                              | 3072-bit DH<br>key                    | The public key is<br>received as part of<br>the key<br>establishment<br>process.  | No output.<br>Only the key<br>fingerprint is sent<br>to the<br>management<br>system for the<br>pairing process. | Internal module<br>(encrypted with<br>Storage<br>extension key) | Tamper protected<br>by automated<br>zeroization of the<br>storage-extension<br>key in the security<br>chip. Zeroization<br>per command.<br>Zeroization when<br>starting new<br>pairing process. | Establish session<br>key<br>authentication |

| DH<br>ephemeral<br>public key of<br>external<br>device                        | 3072-bit DH<br>key                    | The public key is<br>generated as part of<br>the key<br>establishment<br>process. | No output.                                                                                                      | RAM µCM                                                         | Zeroized after<br>each key-<br>agreement.                                                                                                                                                       | Establish session<br>key<br>authentication |

| Validation<br>keys for new<br>firmware                                        | Set of public<br>4096-bit RSA<br>keys | Generated by ADVA<br>before firmware<br>signature                                 | Retrievable, no<br>secret, but<br>protected by<br>digital signature                                             | current/new<br>firmware image                                   | Never, but may be<br>revoked by new<br>firmware image                                                                                                                                           | Firmware update,<br>delete old image       |

Table 9: Cryptographic key, CSP and PSP management

N.B. The public and private static DH key is either stored in the security chip in plaintext or in encrypted form in the internal module. For the latter case, the storage extension key is used for key encryption. This storage extension key is stored in the security chip in plaintext. Whenever the security chip detects tampering, all keys in the security chip are zeroized. This storage extension is used in case multiple communication links are established (muxponder).

N.B. In the table above, "CTR\_DRBG" denotes the deterministic random bit generator implemented in 9TCE firmware, whereas "DRBG" in the table above denotes the deterministic random bit generator implemented in the embedded module. The seed and state values of the DRBG of the embedded module have not been listed above, as these were CSPs already regarded during validation of the embedded module (compare cert. #2628 and corresponding security policy).

N.B. In case of a firmware update performed, the resulting new configuration may no longer be validated (unless the 9TCE has been (re-) validated with new firmware version before).

### 7 EMI/EMC

The Module is EMV Class A (business) compliant to the EMI/EMC requirements 47 CFR Part 15 Subpart B (FCC).

### 8 Self-Tests

The 9TCE performs power-up and conditional self-tests as required for FIPS 140-2 for verification of the integrity of firmware and operation of the implemented FIPS approved algorithms. The same self-tests can also be executed on demand.

Conditional self-tests run automatically when an applicable security function or operation is used.

### 8.1 Power-On or on Demand Self-Tests

Power-on self-tests run automatically after the device powers up with no further input or action of an operator. The module inhibits all data outputs while is in the self-test state.

The module enter approved mode only when all self-tests are successfully passed otherwise the module enters the error state.

The module uses cryptographic algorithm known-answer tests (KAT) to test for each FIPS 140-2-approved cryptographic functions (encryption, decryption, authentication, and random number generation) implemented on the module.

| Function tested                                                                 | Used for                                                                                                          | Self-Test                                                                                                                                | State when fail |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| AES-ECB encryption /<br>decryption on microcontroller<br>(uCM)<br>#C666 / #A886 | Pseudo random number<br>generation<br>Data encryption and decryption<br>in ECB mode for secure storage<br>of CSPs | Known answer test                                                                                                                        | Error           |

| AES-ECB encryption on FPGA<br>#C667 / #A887                                     | Data encryption in CTR mode                                                                                       | Known answer test                                                                                                                        | Error           |

| DRBG of embedded module<br>#455                                                 | Random number generation                                                                                          | Power-on self-test as<br>implemented in embedded<br>module (validated under CMVP<br>cert. #2628),<br>SP 800-90B test,<br>Chi-square test | Error           |

| CTR_DRBG<br>#C666 / #A886                                                       | Random number generation                                                                                          | SP .800-90Ar1 health tests (KAT<br>for instantiate, reseed, and<br>generate functions),<br>Chi-square test                               | Error           |

| SHA-256 hash on uCM<br>#C666 / #A886                                            | Password hash generation<br>Digital signature on FW Image                                                         | Known answer test                                                                                                                        | Error           |

| SHA-512 hash on uCM<br>#C666 / #A886                                            | Key-derivation function                                                                                           | Known answer test                                                                                                                        | Error           |

| HMAC-SHA-256<br>#C666 / #A886                                                   | Key-confirmation                                                                                                  | Known answer test                                                                                                                        | Error           |

| DH<br>#C666 / #A886                                                             | Used for key agreement                                                                                            | Known answer test per IG D.8:<br>Shared Secret Computation KAT<br>-> FPGA expt mod KAT                                                   | Error           |

|                           |                                              | Key Derivation Function (KDF)<br>KAT -> SHA512 KAT |       |

|---------------------------|----------------------------------------------|----------------------------------------------------|-------|

| RSA-3072<br>#C666 / #A886 | Used for firmware signature and verification | Known answer test                                  | Error |

| Firmware                  | FW Checksum<br>CRC 32                        | Known answer test                                  | Error |

Table 10: Power-up self-tests

### 8.2 Conditional Self-Tests

The module implements the following conditional self-tests.

| Function                                                                                | Used for                    | Test                                                                                                                            | State when fail                                                                         | Test is triggered                                         |

|-----------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Generate static or<br>ephemeral DH key pair<br>(Safe Primes Key<br>Generation)<br>#A886 | Key-agreement               | Full public-key validation<br>(Safe Primes Key<br>Verification)                                                                 | Error                                                                                   | For each new<br>generated static or<br>ephemeral key pair |

| Generate static DH key<br>pair<br>#A886                                                 | Key agreement               | Perform shared secret<br>computation with a<br>temporary, randomly<br>selected key pair and verify<br>common result             | Retry                                                                                   | For each new<br>generated static key<br>pair              |

| Received static or<br>ephemeral DH public key<br>#A886                                  | Key-agreement               | Full public-key validation<br>(Safe Primes Key<br>Verification)<br>Check failed three times                                     | > = 3 then Limited<br>encryption<br>Retry (wait for next<br>scheduled key<br>agreement) | For each new public<br>DH key received                    |

| Key confirmation<br>#C666 / #A886                                                       | Key agreement               | HMAC check failed three<br>times                                                                                                | > = 3 then Limited<br>encryption<br>Retry (wait for next<br>scheduled key<br>agreement) | For each key-<br>agreement                                |

| DRBG of embedded<br>module<br>#455                                                      | Random number<br>generation | Self-test as implemented in<br>embedded module<br>(validated under CMVP<br>cert. #2628),<br>SP 800-90B test,<br>Chi-square test | Error and mitigation to<br>Limited encryption                                           | Internally in the<br>embedded module<br>(#2628)           |

| Function                            | Used for                               | Test                                                 | State when fail                               | Test is triggered                                                      |

|-------------------------------------|----------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------|

| CTR_DRBG<br>#C666 / #A886           | Random number<br>generation            | SP 800-90Ar1 health tests,<br>Chi-square test        | Error and mitigation to<br>Limited encryption | For each new<br>generated random<br>number                             |

| CSPs storage in secure IC           | Authentication                         | CRC checksum verification                            | Error                                         | When CSPs are stored in the secure IC                                  |

| Firmware Signature<br>#C666 / #A886 | Firmware update signature verification | Firmware load test (RSA 4096 signature verification) | Stay in current image                         | When the<br>software/firmware<br>update functionality is<br>requested. |

Table 11: Conditional tests

N.B. In case of a firmware update performed, the resulting new configuration may no longer be validated (unless the 9TCE has been (re-) validated with new firmware version before).

### 8.3 Self-Test Failure Handling

On power-on or at any time on demand a self-test can be executed. If this test fails, the module goes into "Error State" and disables cryptographic functions with CSPs, only status information is available.

On failed conditional tests the module may enter either "Error State" or "Limited encryption", depending on the cause of failure (see table 10 above). In case of 'Limited encryption', encrypted data transmission continues until the configured session-key lifetime is reached.

In error state the module LED illuminate red. Forced self-test on demand or power-cycle may return the module to normal operation. State changes are logged.

### 9 Access Control Policy

An access control policy to the module shall be established by the CO in a manner, to prevent unauthorized access to information and services

### 10 Physical Security Policy

### 10.1 Physical Security Mechanisms

It is assumed that the cryptographic module, i.e. the 9TCE mounted in one of the shelves as listed in table 1, is used in a protected environment, where an attacker has only limited time and equipment (FIPS 140-2, security level 2).

The Crypto Officer is responsible for secure configuration, management and changes for setting up the module to the FIPS Approved mode.

| Physical                                                                              | Recommended Frequency of                                                                                                                                                                   | Inspection / Test                                                                                                                                                          |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security Mechanisms                                                                   | Inspection / Test                                                                                                                                                                          | Guidance Details                                                                                                                                                           |

| Seals protecting against opening of the metal shield without leaving visible damages. | First after initial installation and seal<br>placement.<br>Later every time when the module was<br>potentially accessed by unauthorized<br>people, e.g. during cleaning or<br>maintenance. | Visual inspection by the CO of entire metal<br>shield and all seals for damages and signs of<br>removal or tampering. Includes verification of<br>the seal serial numbers. |

Table 12: Inspection/testing of physical security mechanisms

### 11 Security Rules

Summarized, the 9TCE was designed to enforce the following security rules:

- The module grants no access to any cryptographic services without successful (role-based) operator authentication.

- New authentication to the module is required after a power-cycle.

- The module provides two distinct operator roles. The role 'User' (i.e., a remote module of the same type) is authenticated via a Pairing Token. The role 'User' shall use the approved cryptographic function of the module.

- The role 'Crypto Officer' is authenticated via a password. Only the 'Crypto Officer' is allowed to change security-related values.

- The module performs power-on and conditional self-tests. The Crypto Officer is able to start/restart self-tests on demand.