# **Evaluation of the Finalists & Selection of Ascon**

NIST Lightweight Cryptography Team Presenter: Meltem Sönmez Turan

The Sixth Lightweight Cryptography Workshop – June 21, 2023

### **Overview of the Talk**

**II.** Finalists

### **III.** Evaluation of finalists

**IV.** Selection and next steps

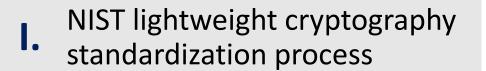

### Part I – NIST Lightweight Cryptography Standardization Process

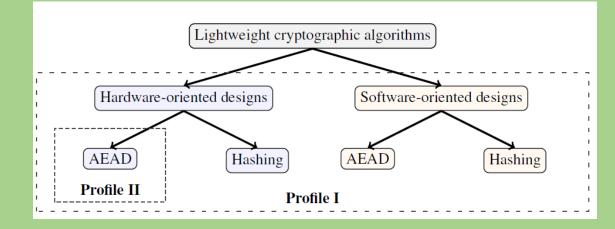

Submission Call (August 2018 – April 2019)

Round 1 (April 2019 – August 2019)

Round 2 (August 2019 – March 2021)

Final Round (March 2021 – February 2023)

#### Workshops:

- First Lightweight Cryptography Workshop July 20 – 21, 2015

- Second Lightweight Cryptography Workshop

October 17 18, 2016

to get feedback on target applications, industry need, requirements, etc.

#### **Publications:**

- NISTIR 8114 *Report on Lightweight Cryptography*

- (White paper, retired) *Profiles for the Lightweight Cryptography Standardization Process*

Submission Call (August 2018 – April 2019)

Round 1 (April 2019 – August 2019)

Round 2 (August 2019 – March 2021)

Final Round (March 2021 – February 2023) **Process:** Public competition-like process with multiple rounds like AES, SHA-3 and PQC standardization.

**Scope:** Authenticated Encryption and (optional) hashing for constrained software and hardware environments

In August 2018, NIST published 'Submission Requirements and Evaluation Criteria for the Lightweight Cryptography Standardization Process'.

Submission deadline: February 2019

Submission Call (August 2018 – April 2019)

Round 1 (April 2019 – August 2019)

Round 2 (August 2019 – March 2021)

Final Round (March 2021 – February 2023)

#### Around 4 months

56 First-round candidates

Evaluation of the candidates were done based on their security

e.g., distinguishing attacks, practical tag forgeries, domain separation issues, new designs with no third-party analysis etc.

NIST IR 8268 explains how 32 candidates (out of 56) were selected to move forward to the second round. NISTIR 8268

Status Report on the First Round of the NIST Lightweight Cryptography Standardization Process

> Meltem Sönmez Turan Kerry A. McKay Çağdaş Çalık Donghoon Chang Larry Bassham

This publication is available free of charge from: https://doi.org/10.6028/NIST.IR.8268

Submission Call (August 2018 – April 2019)

Round 1 (April 2019 – August 2019)

Round 2 (August 2019 – March 2021)

Final Round (March 2021 – February 2023)

#### Around 20 months

32 Second-round candidates

#### Workshops:

- Third Lightweight Cryptography Workshop November 4 – 6, 2019

- Fourth Lightweight Cryptography Workshop 2016

October 19 21, 2020

**NIST IR 8369** explains how 10 finalists were selected to move forward to the final round. NISTIR 8369

Status Report on the Second Round of the NIST Lightweight Cryptography Standardization Process

> Meltem Sönmez Turan Kerry McKay Donghoon Chang Çağdaş Çalık Lawrence Bassham Jinkeon Kang John Kelsey

This publication is available free of charge from: https://doi.org/10.6028/NIST.IR.8369

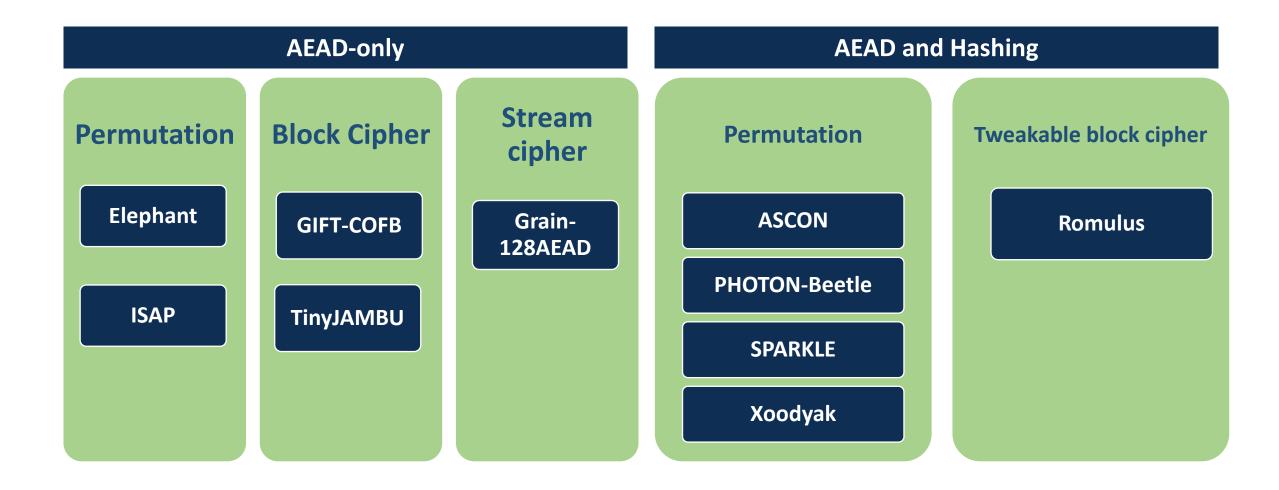

# Part II – Finalists

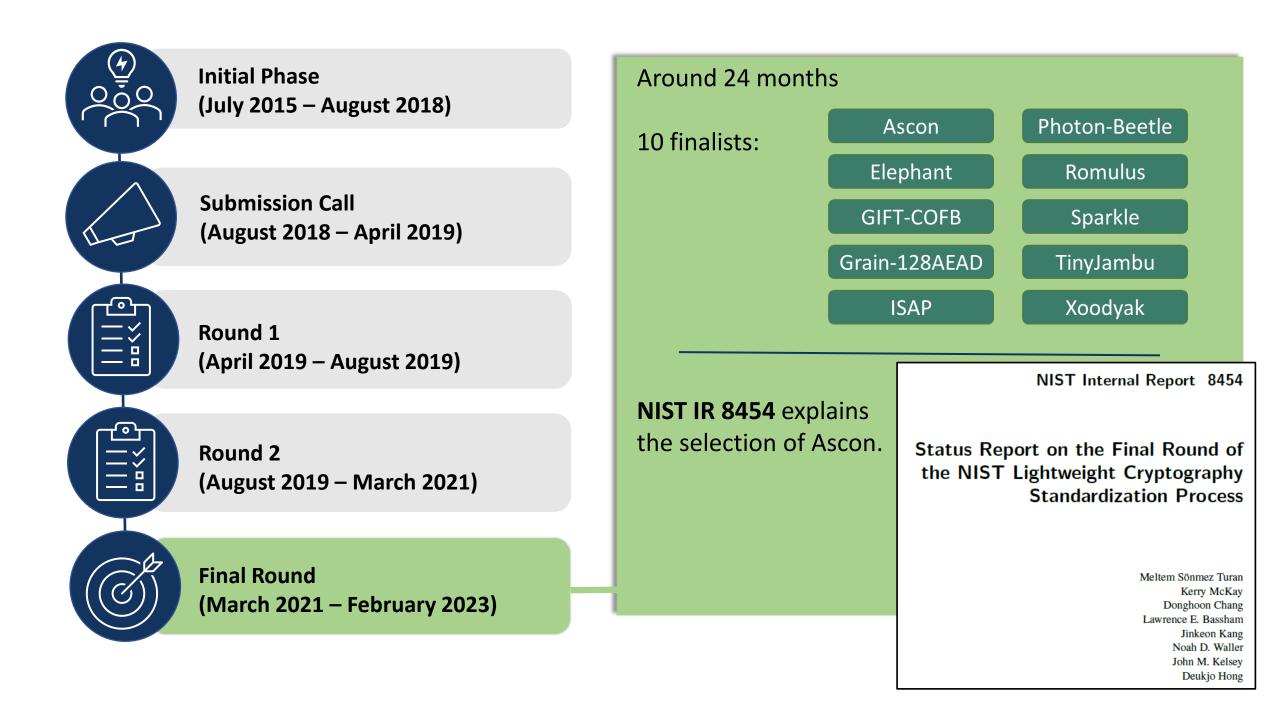

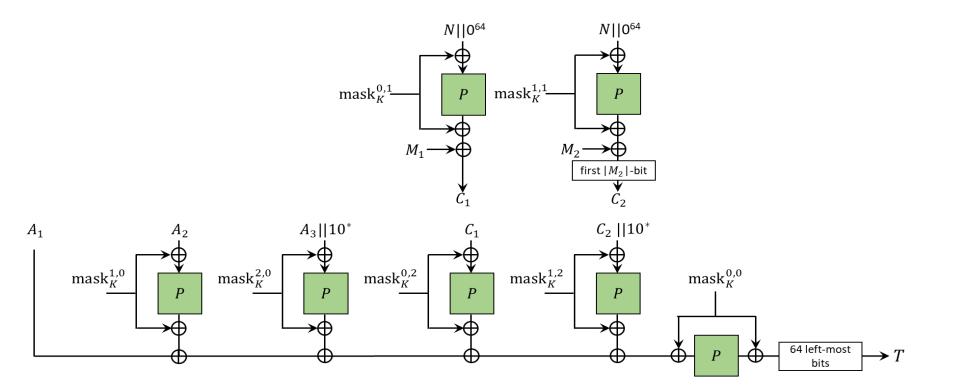

- Permutation-based (320-bit) AEAD and hashing scheme (fixed or variable output length)

- MonkeyDuplex mode with keyed initialization and finalization

- No design tweak, new variant added in the final round

- Included in the final portfolio of CAESAR for lightweight authenticated encryption

|      | Variant     | Parameter sizes                |  |

|------|-------------|--------------------------------|--|

|      | Ascon-128   | 128-bit key/nonce/tag          |  |

| AEAD | Ascon-128a  | 128-bit key/nonce/tag          |  |

|      | Ascon-80-pq | 160-bit key, 128-bit nonce/tag |  |

| Hash | Ascon-hash  | 256-bit digest                 |  |

| На   | Ascon-hasha | 256-bit digest                 |  |

| XOF  | Ascon-XOF   | Arbitrary length digest        |  |

| ×    | Ascon-XOFa  | Arbitrary length digest        |  |

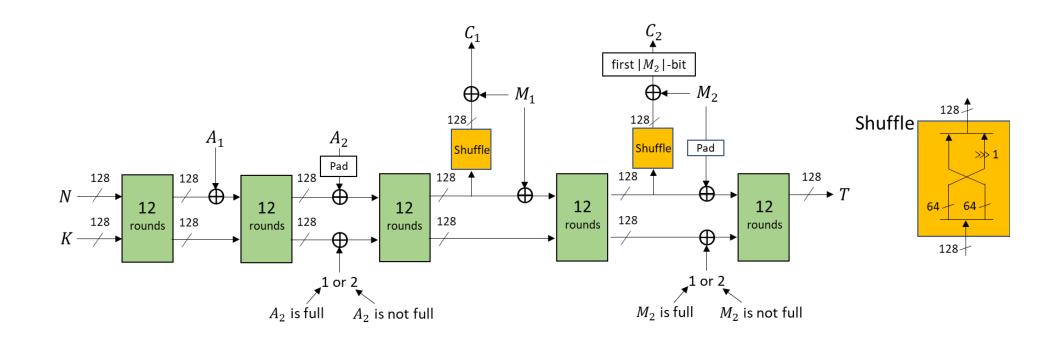

- Nonce-based Encrypt-then-MAC mode

- Only finalist with a parallel mode

- Design tweak: Mode slightly modified to achieve authenticity under nonce-reuse.

| Variant  | Parameter sizes                        |

|----------|----------------------------------------|

| Dumbo    | 128-bit key, 96-bit nonce, 64-bit tag  |

| Jumbo    | 128-bit key, 96-bit nonce, 64-bit tag  |

| Delirium | 128-bit key, 96-bit nonce, 128-bit tag |

- Block-cipher (GIFT-128) based AEAD scheme

- Combined Feedback (COFB) mode

- No design tweak

| Variant   | Parameter sizes       |

|-----------|-----------------------|

| Gift-COFB | 128-bit key/nonce/tag |

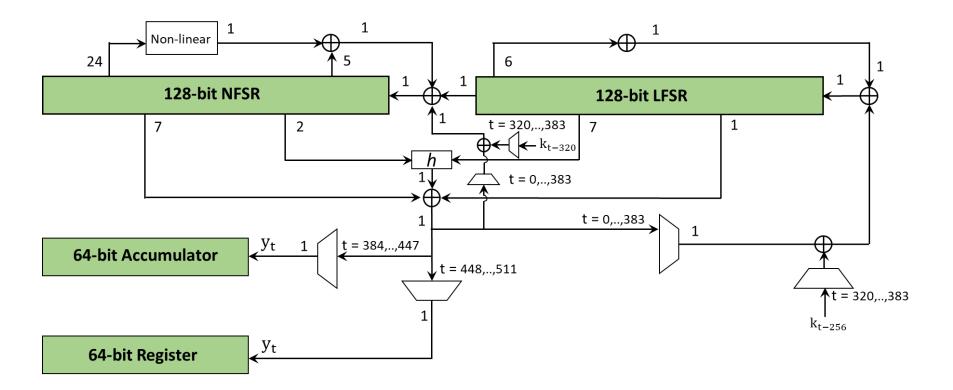

- Feedback shift register based AEAD scheme

- Design tweak on the initialization part

- (Earlier versions) Part of eSTREAM portfolio, included in ISO/IEC 29167-13:2005

| Variant       | Parameter sizes                       |

|---------------|---------------------------------------|

| Grain-128AEAD | 128-bit key, 96-bit nonce, 64-bit tag |

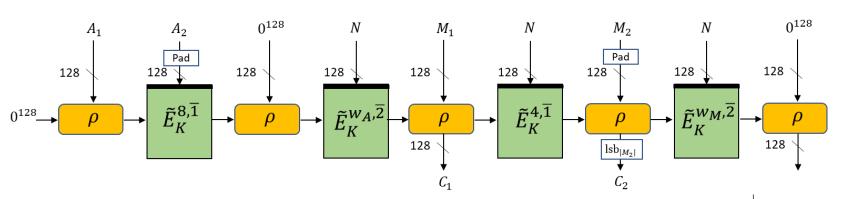

- Permutation-based (Ascon and Keccak permutations) AEAD scheme

- Can be paired with Ascon Hash

- Nonce-based Encrypt-then-MAC mode

- Algorithm-level security against implementation attacks

- No design tweak (primary variant updated)

| Variant     | Parameter sizes       |  |

|-------------|-----------------------|--|

| ISAP-A-128a | 128-bit key/nonce/tag |  |

| ISAP-K-128a | 128-bit key/nonce/tag |  |

| ISAP-A-128  | 128-bit key/nonce/tag |  |

| ISAP-K-128  | 128-bit key/nonce/tag |  |

- Family of permutation-based (256-bit Photon permutation) AEAD & hashing scheme

- Sponge-like mode with a combined feedback.

- No design tweak

|      | Variant                     | Parameter sizes       |

|------|-----------------------------|-----------------------|

| AEAD | Photon-Beetle-<br>AEAD[128] | 128-bit key/nonce/tag |

|      | Photon-Beetle-<br>AEAD[32]  | 128-bit key/nonce/tag |

| Hash | Photon-Beetle-<br>Hash[32]  | 256-bit digest        |

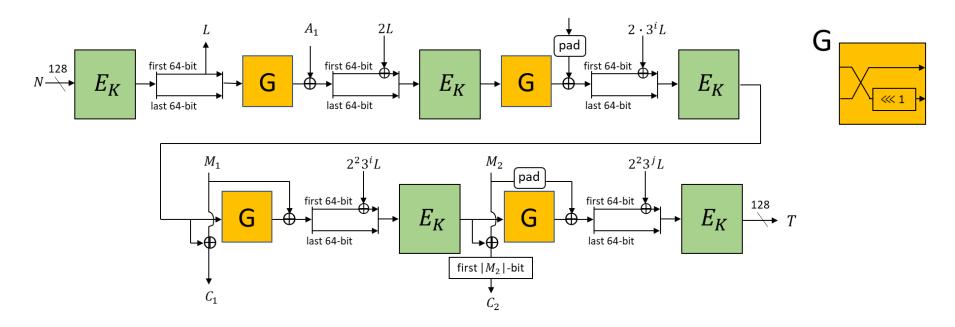

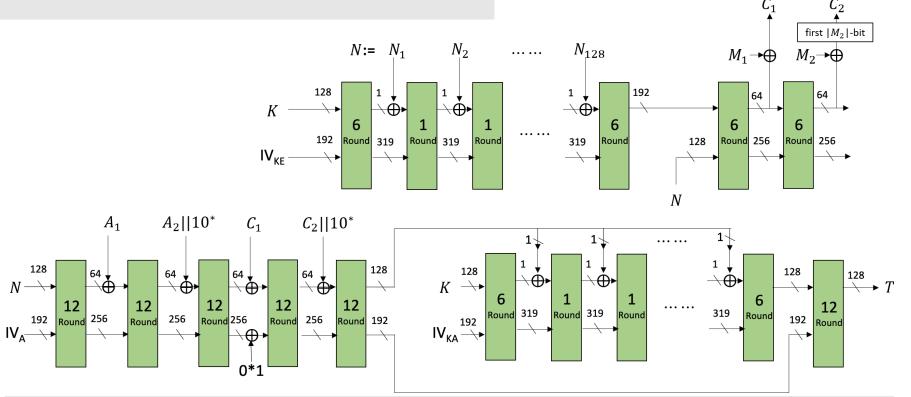

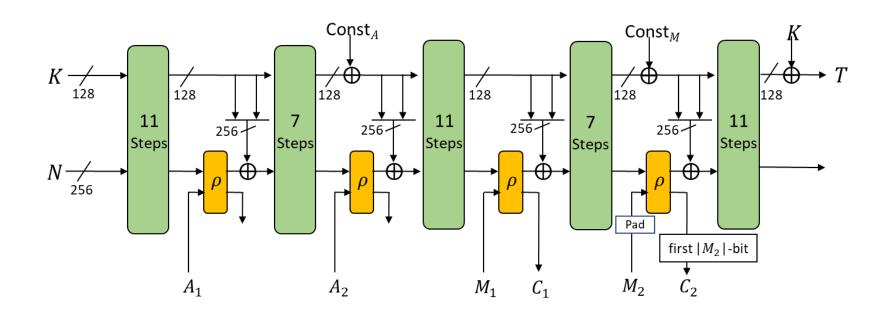

- Family of tweakable-block-cipher (Skinny) based AEAD & hashing

- Romulus-N: rate-1 TBC-based combined feedback, Romulus-M: MAC-then-Encrypt

- Nonce-misuse and nonce-respecting variants

- Design tweak to reduce the number of rounds from 56 to 40, removal of non-primary variants, addition of new variants.

|      | Variant   | Parameter sizes       |  |

|------|-----------|-----------------------|--|

|      | Romulus-N | 128-bit key/nonce/tag |  |

| AEAD | Romulus-M | 128-bit key/nonce/tag |  |

|      | Romulus-T | 128-bit key/nonce/tag |  |

| Hash | Romulus-H | 256-bit digest        |  |

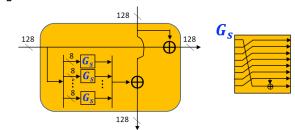

- Family of permutation-based AEAD (SCHWAEMM) and hashing (ESCH)

- ARX based design

- Sponge construction with combined feedback

- Tweak to change the primary variant

|      | Variant         | Parameter sizes                |  |

|------|-----------------|--------------------------------|--|

|      | SCHWAEMM256-128 | 128-bit key/tag, 256-bit nonce |  |

| AD   | SCHWAEMM128-128 | 128-bit key/nonce/tag          |  |

| AEAD | SCHWAEMM192-192 | 192-bit key/nonce/tag          |  |

|      | SCHWAEMM256-256 | 256-bit key/nonce/tag          |  |

| Hash | ESCH256         | 256-bit digest                 |  |

| На   | ESCH384         | 384-bit digest                 |  |

| ЪF   | XOESCH256       | Arbitrary length digest        |  |

| XOF  | XOESCH384       | Arbitrary length digest        |  |

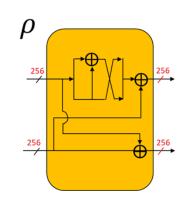

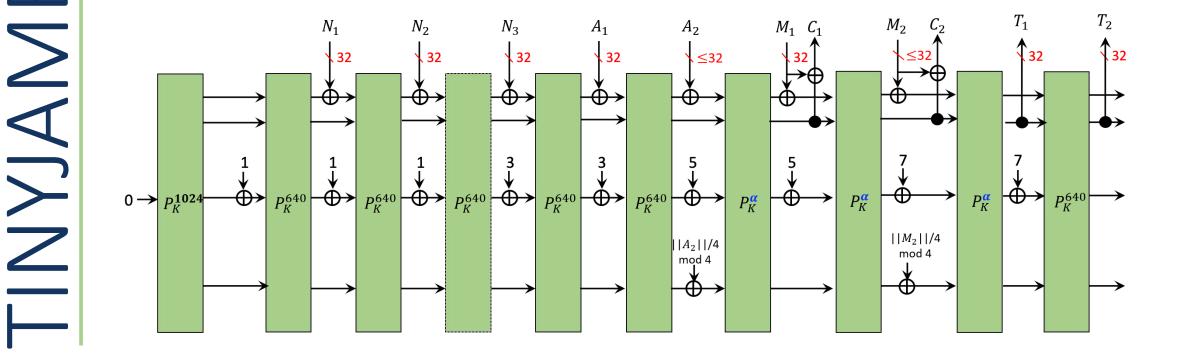

- Keyed-permutation based AEAD scheme

- Uses 128-bit nonlinear feedback shift register

- Inspired by JAMBU (CAESAR candidate)

- Design tweak: increase in number of rounds to improve security margin.

| Variant       | Parameter sizes                       |  |

|---------------|---------------------------------------|--|

| TinyJambu-128 | 128-bit key, 96-bit nonce, 64-bit tag |  |

| TinyJambu-192 | 192-bit key, 96-bit nonce, 64-bit tag |  |

| TinyJambu-256 | 256-bit key, 96-bit nonce, 64-bit tag |  |

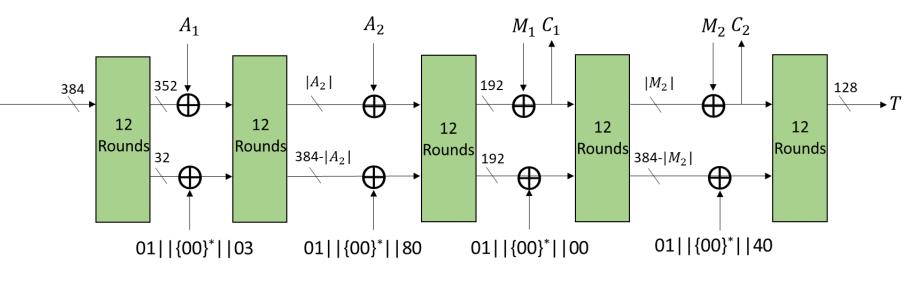

- Family of permutation based AEAD & hashing scheme

- Based on 384-bit Xoodoo permutation

- Uses Cyclist mode

- Design tweak: simplified initialization to improve performance for short messages

|      | Variant | Parameter sizes         |

|------|---------|-------------------------|

| AEAD | Xoodyak | 128-bit key/nonce/tag   |

| Hash | Xoodyak | 256-bit digest          |

| XOF  | Xoodyak | Arbitrary length digest |

$K | |N| | (byte-length of N) | |01| | {00}^* | |02$

### **Underlying Components and Functionalities**

### Variants of the Finalists

| Finalist      | # Variants       | Key size<br>(bits) | Nonce size<br>(bits) | Tag size<br>(bits) | Digest<br>size (bits) |

|---------------|------------------|--------------------|----------------------|--------------------|-----------------------|

| Ascon         | 3 AEAD<br>2 hash | 128 - 160<br>      | 128<br>              | 128<br>            | <br>256               |

| Elephant      | 3 AEAD           | 128                | 96                   | 64-128             |                       |

| GIFT-COFB     | 1 AEAD           | 128                | 128                  | 128                |                       |

| Grain-128aead | 1 AEAD           | 128                | 96                   | 64                 |                       |

| ISAP          | 4 AEAD           | 128                | 128                  | 128                |                       |

| PHOTON-Beetle | 2 AEAD<br>1 hash | 128<br>            | 128<br>              | 128<br>            | <br>256               |

| Romulus       | 3 AEAD<br>1 hash | 128<br>            | 128<br>              | 128<br>            | <br>256               |

| Sparkle       | 4 AEAD<br>2 hash | 128-256<br>        | 128-256<br>          | 128-256<br>        | <br>256-384           |

| TinyJambu     | 3 AEAD           | 128-256            | 96                   | 64                 |                       |

| Xoodyak       | 1 AEAD<br>1 hash | 128<br>            | 128<br>              | 128<br>            | <br>256               |

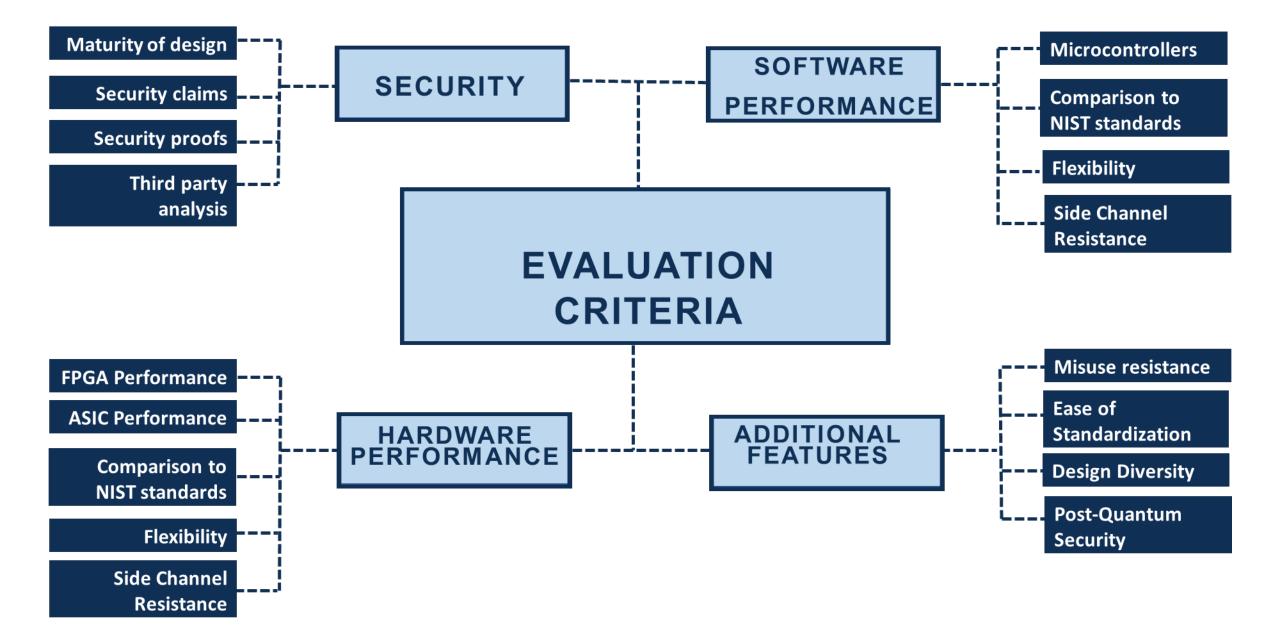

## Part III – Evaluation and Selection

### **Security Requirements**

The submission call included the security requirements:

- Key size is at least 128-bit.

- The limits on the input sizes (e.g., message, AD) is at least 2<sup>50</sup>-1 bytes.

- Any nonce-respecting attack on the AEAD with 128-bit key requires at least 2<sup>112</sup> time complexity on a classical computer in the single-key setting.

(For 256 bit key, time complexity of at least 2<sup>224</sup>, if applicable.)

- Any attack on the hash function variants requires at least 2<sup>112</sup> time complexity on a classical computer (if applicable).

### **Security Margins and Claims and Maturity**

- All finalists have met the security requirements and provided sufficient security margins.

- None of the security claims made by the submitters have been invalidated.

- Maturity of the design is one of the important security evaluation factors.

- Is the finalist based on well-established design principles?

- Did the finalist receive enough third-party analysis?

- Are there design tweaks that invalidate the earlier security analysis?

- Are there any additional concerns (e.g., nonce misuse, related-key, RUP security, post quantum)?

### **Security Evaluations of the Finalists**

**Ascon:** Received large number of third-party analysis. High security margin. Best key-recovery attack on 7 (out of 12) rounds of initialization. Distinguishers on full permutation.

**Elephant:** High security margin. Best distinguisher\* on 160-bit Spongent permutation covers 40 (out of 80) rounds. Some results on Even-Mansour construction in the quantum setting.

**GIFT-COFB:** Large number of third-party analysis on GIFT. Best key-recovery attack on GIFT-128 covers 27 (out of 40) rounds. High security margin. Some level of nonce-misuse resilience.

**Grain-128AEAD:** Large number of third-party analysis on *earlier* versions. Tweaked in response to the state-recovery observation. Best key-recovery attack\* covers 192 (out of 512) rounds of initialization. High security margin.

**ISAP:** Large number of third-party analysis on Ascon permutation. Best forgery attack covers 4 (out of 12) rounds. High security margin.

\*Requires time complexity beyond the time limit made by the submitters.

### **Security Evaluations of the Finalists**

**Photon-Beetle:** No analysis on round-reduced Photon-Beetle-AEAD. Distinguishing attack on the permutation covers 10 (out of 12) rounds.

**Romulus:** High security margin. Number of rounds reduced from 56 to 40. Best keyrecovery attacks\* on Skinny with 32 (out of 40) rounds in the related-key setting. Nonce misuse resistance. For hash variant, preimage attack\* on 23 (out of 40) rounds.

**Sparkle:** High security margin. Best key-recovery attack\* covers 4.5 (out of 11) steps of 384-bit permutation without whitening. No known results on the hash variants. Distinguishers\* on permutation up to 6 steps.

**TinyJambu:** Tweak to increase the number of rounds. Weak-key distinguishing attack covers 476 (out of 1024) rounds. Forgery attacks on full-round TinyJambu-192 and TinyJambu-256 in the related-key setting.

**Xoodyak:** Best key recovery attack covers 6 (out of 12) rounds. High security margin.

\*Requires time complexity beyond the time limit made by the submitters.

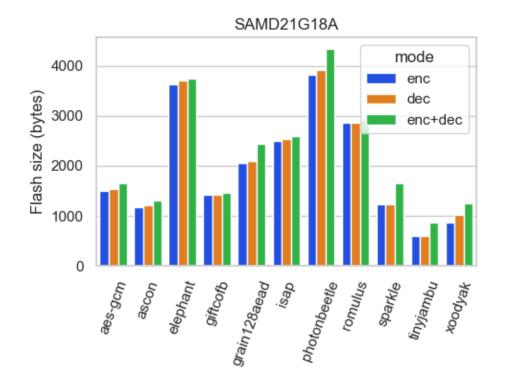

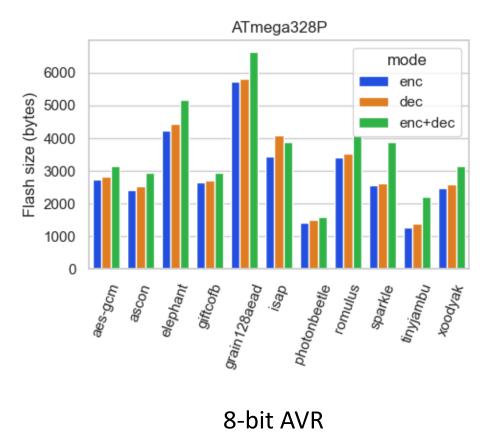

### **Software Benchmarking**

### **Software Benchmarking**

Microcontroller benchmarking by NIST LWC Team

#### **Devices:**

- 8-bit AVR

- 32-bit ARM Cortex M0+, M4, M3

- MIPS32 M4K

- Tensilica L106

#### **Metrics:**

- Code size

- Execution time

Microcontroller benchmarking by Renner et al.

#### **Devices:**

- 8-bit AVR

- 32-bit ARM Cortex M3, M7

- Tensilica Xtensa LX6

- RISC-V

#### Metrics:

- Speed

- Code Size

- RAM usage

Microcontroller benchmarking by Weatherly

#### **Devices:**

- AVR

- ARM Cortex-M3

- Tensilica Xtensa LX6

#### Metrics:

• Speed

eBACS (ECRYPT Benchmarking of Cryptographic Systems) by Lange and Bernstein

#### **Devices:**

Many systems covering ARM, AMD, Intel, PPC, RISC V, and MIPS architectures

#### **Metrics:**

• Speed

### **Available Implementations**

| Finalist      | #AEAD | #Hash | #Combined | Total |

|---------------|-------|-------|-----------|-------|

| Ascon         | 120   | 110   | 52        | 282   |

| Elephant      | 6     | -     | -         | 6     |

| GIFT-COFB     | 11    | -     | -         | 11    |

| Grain-128AEAD | 6     | -     | -         | 6     |

| ISAP          | 37    | 1     | 4         | 42    |

| PHOTON-Beetle | 20    | 10    | 16        | 46    |

| Romulus       | 32    | 11    | 27        | 70    |

| Sparkle       | 25    | 13    | 3         | 41    |

| TinyJambu     | 9     | -     | -         | 9     |

| Xoodyak       | 9     | 8     | 1         | 18    |

| Total         | 275   | 153   | 103       | 531   |

### Size comparisons

32-bit ARM Cortex-M0+

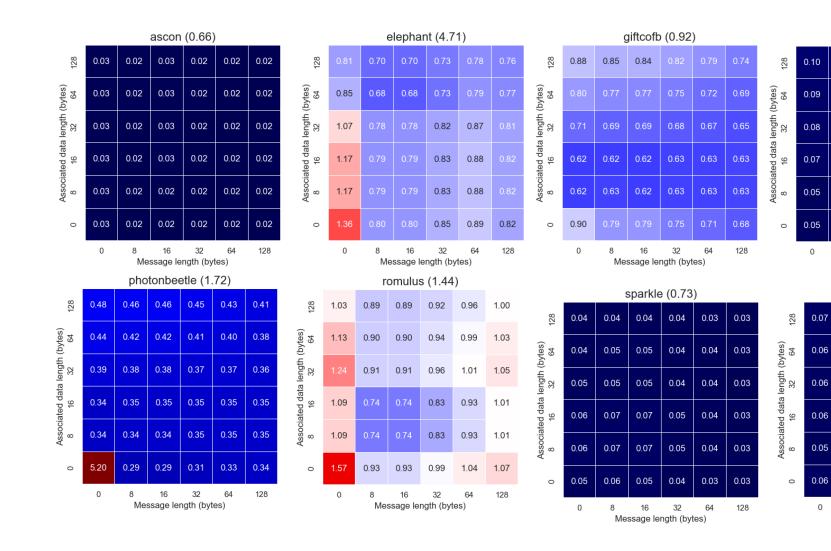

### **Execution time comparison to AES**

|      |                                              |      |         | ioup (         | 1.44)           |           |

|------|----------------------------------------------|------|---------|----------------|-----------------|-----------|

| 0.08 | 128                                          | 0.20 | 0.26    | 0.27           | 0.25            | 0.22      |

| 0.08 | (bytes)<br>64                                | 0.26 | 0.33    | 0.34           | 0.30            | 0.26      |

| 0.07 | Associated data length (bytes)<br>8 16 32 64 | 0.32 | 0.40    | 0.42           | 0.35            | 0.28      |

| 0.07 | ited data                                    | 0.39 | 0.46    | 0.48           | 0.39            | 0.30      |

| 0.07 | Associa<br>8                                 | 0.37 | 0.45    | 0.47           | 0.38            | 0.29      |

| 0.07 | 0                                            | 0.51 | 0.55    | 0.58           | 0.44            | 0.32      |

| 128  |                                              | 0    | 8<br>Me | 16<br>ssage le | 32<br>ngth (byt | 64<br>es) |

|      |                                              |      |         |                |                 |           |

grain128aead (2.53)

0.09

0.09

0.08

0.07

0.06

0.06

16

0.07

0.06

0.06

0.06

0.06

0.06

16

Message length (bytes)

tinyjambu (0.36)

0.07

0.07

0.06

0.06

0.06

0.06

32

Message length (bytes)

0.09

0.08

0.07

0.06

0.05

0.05

8

0.06

0.06

0.05

0.05

0.04

0.05

8

0.09

0.08

0.08

0.07

0.06

0.06

32

0.09

0.08

0.07

0.07

0.06

0.07

64

0.07

0.07

0.07

0.07

0.06

0.07

64

0.07

0.07

0.07

0.07

0.06

0.07

128

isap (1.44)

0.21

0.22

0.23 30

0.22

0.23 32

128

| _                                            | xoodyak (1.85) |      |      |      |      |      |

|----------------------------------------------|----------------|------|------|------|------|------|

| 128                                          | 0.14           | 0.12 | 0.12 | 0.13 | 0.12 | 0.12 |

| (bytes)<br>64                                | 0.18           | 0.14 | 0.14 | 0.15 | 0.14 | 0.13 |

| Associated data length (bytes)<br>8 16 32 64 | 0.20           | 0.15 | 0.15 | 0.15 | 0.14 | 0.13 |

| ated data<br>16                              | 0.26           | 0.18 | 0.18 | 0.18 | 0.15 | 0.14 |

| Associ<br>8                                  | 0.26           | 0.18 | 0.18 | 0.18 | 0.15 | 0.14 |

| 0                                            | 0.38           | 0.22 | 0.22 | 0.21 | 0.17 | 0.15 |

| 0 8 16 32 64 128<br>Message length (bytes)   |                |      |      | 128  |      |      |

Execution time ratio of smallest primary AEAD implementations to AES-GCM on nRF52840

### **Summary of Results**

A group of candidates emerged as having compact and fast implementations across software platforms and studies (listed alphabetically)

| AEAD      | Hashing | AEAD + hashing |

|-----------|---------|----------------|

| Ascon     | Ascon   | Ascon          |

| GIFT-COFB | SPARKLE | SPARKLE        |

| SPARKLE   | Xoodyak | Xoodyak        |

| TinyJAMBU |         |                |

| Xoodyak   |         |                |

### Hardware Benchmarking

### Hardware Benchmarking (Round 2)

| Initiative                | Platforms                                                           | Metrics                                      |  |

|---------------------------|---------------------------------------------------------------------|----------------------------------------------|--|

|                           | 37111 4 21 77                                                       | Resource utilization (LUT or LE, flip-flops) |  |

| GMU CERG group [270]      | Xilinx Artix-7<br>Intel Cyclone 10 LP<br>Lattice Semiconductor ECP5 | Maximum clock frequency (MHz)                |  |

|                           |                                                                     | Throughput (Mbits/s)                         |  |

|                           |                                                                     | Energy per bit (nJ/bit)                      |  |

|                           |                                                                     | Area ( $\mu m^2$ and GE)                     |  |

| Khairallah et al. [274]   | TSMC 65nm<br>FDSOI 28nm                                             | Clock period (ns)                            |  |

|                           |                                                                     | Power (mW)                                   |  |

|                           |                                                                     | Energy (mJ)                                  |  |

|                           | ST Micro 65nm                                                       | Throughput (bits per cycle)                  |  |

|                           | TSMC 65nm                                                           | Area (GE)                                    |  |

| Aagaard and Zidarič [276] | ST Micro 90nm                                                       | Energy (nJ)                                  |  |

|                           | TSMC 90nm                                                           | Area×Energy (GE×nJ)                          |  |

|                           | ARM/IBM 130nm                                                       | Clock Speed (GHz)                            |  |

Top performers across hardware technologies and studies (listed alphabetically)

| Area      | Energy    | Throughput |

|-----------|-----------|------------|

| Ascon     | Ascon     | Ascon      |

| GIFT-COFB | GIFT-COFB | GIFT-COFB  |

| Romulus   | TinyJAMBU | TinyJAMBU  |

| TinyJAMBU | Xoodyak   | Xoodyak    |

Anticipated effects of final round tweaks:

- Romulus and Xoodyak: tweaked to increase performance.

Decrease energy, increase throughput.

- TinyJambu tweaked to increase security Increase energy, decrease throughput

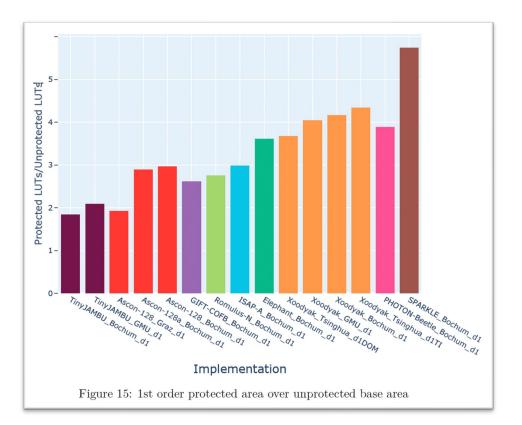

## **Protected Implementations**

### **Protected Implementations**

In January 2022, GMU organized effort to evaluate protected hardware and software implementations and published three calls:

- Call for Protected Hardware Implementations

- Call for Protected Software Implementations

- Call for Side-Channel Security Evaluation Labs

Benchmarked implementations with  $1^{st}$ ,  $2^{nd}$ , and  $3^{rd}$  order masking.

TinyJAMBU, Ascon, and GIFT-COFB had lowest first-order protected area over base area.

### Part IV – Selection and Next Steps

### **Selection Process**

Fair evaluation of finalists is challenging

- Assigning different weights for different criteria (security, performance in software and hardware, design maturity, amount of third-party analysis, IP issues, etc.)

- Different security claims, different functionality, attacks with different complexities etc.

- Limited resources (not all algorithms got the same attention from the crypto community) for security analysis and benchmarking.

Decision relied on publicly available analysis and benchmarking results.

### **Selection of Ascon**

In February 2023, NIST announced the Ascon family as the winner.

- High security margin, large number of third-party analysis

- No design tweaks

- Primary choice for the for lightweight applications in the final CAESAR portfolio

- Mode-level protection mechanism for security against leakage.

- Support for additional functionalities XOF, dedicated MAC, in addition to Hash

- Performs better than the NIST standards in hardware and software benchmarks

- Implementation and design flexibility

- Lower additional cost for protected implementations

$\mathcal{O}$ **'** 7

Getting feedback on standardization details

Publication of draft standards (later in 2023)

NATIONAL INSTITUTE OF STANDARDS AND TECHNOLOGY U.S. DEPARTMENT OF COMMERCE

# **CONTACT US**

lightweight-crypto@nist.gov

**PUBLIC FORUM** lwc-forum@list.nist.gov

**GITHUB** https://github.com/usnistgov/Lightweight-Cryptography-Benchmarking

**WEBSITE** https://csrc.nist.gov/Projects/lightweight-cryptography